# Programmable switched current filters using MOSFET-only current dividers

R. T. Gonçalves, S. Noceti Filho, M. C. Schneider, C. Galup-Montoro

Laboratório de Instrumentação Eletrônica - Departamento de Engenharia Elétrica

Universidade Federal de Santa Catarina - C. P. 476

88 040 900 - Florianópolis - SC - Brasil

Telephone: 55 48 231 9643 - Fax : 55 48 231 9770

E-mail: carlos@linse.ufsc.br

### ABSTRACT

A new technique to achieve switched current filters is presented. The basic elements of the filters are operational amplifiers, switches, MOS transistors and grounded capacitors. The use of MOSFET-only current dividers allows digitally programming the coefficients of the filter transfer function. User programmable analog filtering in digital CMOS technology and, particularly, in sea-of-gates is the main envisaged application of the proposed technique.

### INTRODUCTION

Switched capacitors (SC) and switched currents (SI) are the sampled data processing techniques in use nowadays. SC filters, usually implemented through double-poly CMOS processes, have performance rarely matched by other types of analog integrated circuits and, as a consequence, have been extensively employed in commercial analog circuits. The driving force behind the development of the SI technique at the end of the last decade [1] was its full compatibility with conventional VLSI processes. However, few circuits using SI techniques have been fabricated to date [2,3]. Therefore, it is hard to conclude about the merit of SI circuits for a wide range of applications. Moreover, the digital programming of conventional analog filters achieved by selecting different combinations of either capacitors [4] or current mirrors [5] requires a large silicon area.

In this paper we show a procedure that employs opamps, MOSFET-only programmable current attenuators [6], switches and capacitors to realize SI filters. This approach to implement programmable filters takes advantage of the reduced area, proportional to the number of bits, of programmable MOSFET-only attenuators. The use of the opamp as the active device allows a simple and modular design of the filter. Even though nonlinear, grounded MOS capacitors [7] are the natural solution to act as memory elements.

## THE SWITCHED CURRENT TECHNIQUE

Sampled-data analog signal processing requires four basic operations: inversion, addition, multiplication and delay. In 0-7803-2972-4/96\$5.00©1996 IEEE

SI circuits, these operations are accomplished by switched current mirrors. Current mirrors realize a nonlinear I-V conversion followed by an inverse V-I conversion, leading to a linear relationship between input and output currents. Fig. 1(a) displays the scheme of the conventional switched current mirror [1].

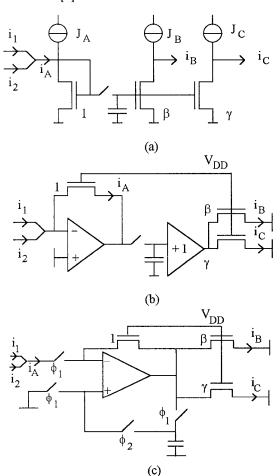

Fig. 1. First generation switched current mirrors

(a) conventional (b) proposed in this work

(c) modified version

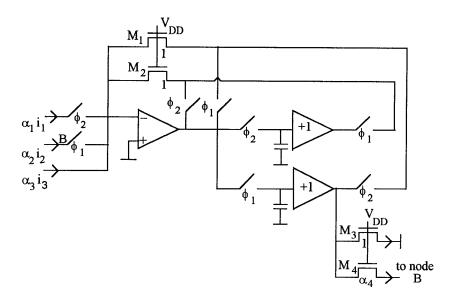

Fig. 2 - Second generation generalized switched current integrator

As shown in Fig. 1(b), a switched current mirror can also be implemented with one MOS transistor connected between the output and the virtual ground of the opamp and another between the output and ground (or a virtual ground of another opamp). With the switch closed, the hold capacitor is charged to a voltage V, which depends on the value of the input current  $i_A$ , the transistor parameters and the gate voltage. The output current is such that  $i_B = -\beta i_A$ , where  $\beta$  is the scale factor. When the switch opens, a voltage equal to V is held on the memory capacitor and the current is sustained at the output. The voltage follower avoids the discharge of the hold capacitor through the output transistors.

In order to reduce the number of operational amplifiers the cell shown in Fig. 1(c), where the clock waveforms are non-overlapping, can be used as an SI mirror. For the three cases presented in Fig. 1 the scale factor  $\beta$  of the current mirrors is equal to the quotient of the aspect ratios of the output and input transistors.

A building block for use in SI filters is the integrator. Fig. 2 shows the generalized second generation SI integrator [8], implemented according to the approach presented in this paper. The analysis of the network in fig. 2 is straightforward, leading to the following z-domain output current:

$$I_{o}(z) = \frac{A_{1}z^{-1}}{1 - Bz^{-1}}I_{1}(z) - \frac{A_{2}}{1 - Bz^{-1}}I_{2}(z)$$

$$\frac{-A_{3}(1 - z^{-1})}{1 - Bz^{-1}}I_{3}(z)$$

(1)

where

$$A_1 = \frac{\alpha_1}{1 + \alpha_4} \qquad A_2 = \frac{\alpha_2}{1 + \alpha_4} \qquad A_3 = \frac{\alpha_3}{1 + \alpha_4}$$

$$B = \frac{1}{1 + \alpha_4}$$

Even though we have shown the application of the new method to implement SI filters through the examples of a delay and an integrator, we can readily extend it to any conventional SI filters [1,2,8].

In order to provide the current mirrors in Figs. 1(b) and 1(c) with digital programmability, MOSFET-only current dividers [6] can be used instead of MOS transistors.

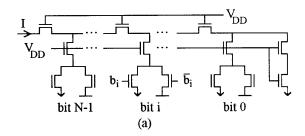

Fig. 3 shows the principle of current division [6,9] for an array of identical transistors, where the current is successively divided by two in the branches of the network. The output current is a fraction of the input current, selected by, say, the ON state of the left side transistors in the parallel connections. This programmable current divider has two big advantages over other digitally programmed dividers: (i) MOSFET's perform simultaneously as elements of the divider network and as switches and (ii) the resistance of the current attenuator is independent of both the number of bits and of the attenuation factor. Moreover, the high linearity of this current division technique [6] has been proved adequate for analog signal processing.

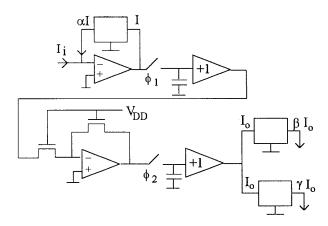

A circuit which delays current samples by one complete clock period is shown in fig 4. This circuit is analogous to the first generation current delay cell, presented in ref. [1]. The inclusion of a current inversion block provides the network with outputs that are non-inverted replicas of the

input current. One of the output currents, delayed from the input current by one clock period is given by

$$\beta I_{\Omega}(z) = (\beta/\alpha)z^{-1}I_{i}(z)$$

(2)

MOSFET-only current divider

$$\alpha = \sum_{i=0}^{N-1} b_i 2^{(i-N)}$$

(b)

Fig. 3 -(a) MOSFET-only binary current divider and (b)its symbol.

A digitally programmable current integrator can be implemented by feeding back a fraction of the output current from a current delay circuit, such as the one shown in Fig. 4. By feeding back, for instance, the output current  $\beta\,I_O$  to the input node, one obtains the z-domain transfer function

$$H(z) = \frac{I_o(z)}{I_i(z)} = \frac{1}{\alpha} \frac{z^{-1}}{1 - \frac{\beta}{\alpha} z^{-1}}$$

(3)

which corresponds to a forward Euler non-inverting lossy integrator if  $(\beta/\alpha) < 1$  or to a lossless integrator if  $(\beta/\alpha) = 1$ .

## **EXPERIMENTAL RESULTS**

A prototype of an SI lossy integrator has been built with NMOS (W=3  $\mu m,\ L=1.2 \mu m)$  integrated transistors and discrete opamps, switches and capacitors. The integrator scheme has been obtained from the delay circuit shown in Fig.4 by feeding back the output current  $\beta$  I $_o$  to the input. The parameters of the network are  $\alpha=1$  and  $\gamma=1-\beta$ .

Therefore, the z-domain transfer function is

$$H(z) = \frac{\gamma I_o(z)}{I_i(z)} = \frac{(1-\beta)z^{-1}}{1-\beta z^{-1}}$$

(4)

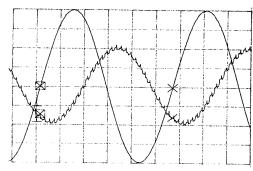

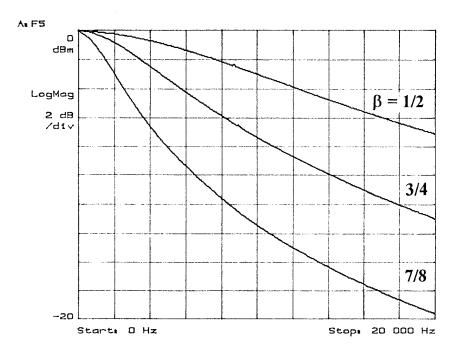

The output of the integrator ( $\beta$ =7/8) for a 3.6 kHz input current is shown in Fig.5 and the measured magnitude responses of the lossy integrator are presented in Fig.6 for  $\beta = 7/8$ , 3/4, 1/2. The measured and the theoretical magnitude responses of the integrator agree very closely.

#### CONCLUSIONS

A new switched current technique, which employs opamps, switches, grounded capacitors and MOSFET's has been described. Three methods regarding the realization of SI filters have been proposed.

The use of MOSFET-only current dividers in the output and feedback of the opamps allows digitally programming the filter coefficients without requiring large silicon areas. Therefore, the proposed technique is very useful for analog programmable filters.

Fig. 4 - Switched current circuit whose outputs are delayed scaled replicas of the input current

# REFERENCES

- J. B. Hughes, N. C. Bird, I. C. MacBeth, "Switched Currents A New Technique for Analog Sampled-Data Signal Processing", IEEE ISCAS, Portland, OR, USA, pp. 1584-1587, May 1989.

- [2] J. B. Hughes, K. W. Moulding, "Switched-Current Signal Processing for Video Frequencies and Beyond", *IEEE J. Solid-State Circuits*, vol. 28, no. 3, pp. 314-322, March 1993.

- [3] P. J. Crawley, G. W. Roberts, "Predicting Harmonic Distortion in Switched-Current Memory Circuits", *IEEE Trans. on Circ. and Syst.*, part II, vol. 41, no. 2, pp. 73-86, February 1994.

- [4] J. F. Duque-Carrillo, J. Silva-Martínez, E. Sánchez-Sinencio, "Programmable Switched Capacitor Bump Equalizer Architecture", IEEE J. Solid-State Circuits, vol.25, no. 4, pp. 1035-1039, August 1990.

- [5] K.-H. Loh et all, "A Versatile Digitally Controlled Continuous-Time Filter Structure with Wide-Range and Fine Resolution Capability", IEEE Trans. on Circ. and Syst., part II, vol. 39, no.5, pp. 265-276, May 1992.

- [6] K. Bult and G. J. G. M. Geelen, "An Inherently Linear and Compact MOST-Only Current Division Technique", *IEEE J. Solid-State Circuits*, vol. 27, no. 12, pp. 1730-1735, December 1992.

- [7] A. T. Behr, M. C. Schneider, S. Noceti Filho, C. G. Montoro, "Harmonic Distortion Caused by Capacitors Implemented with MOSFET Gates", *IEEE J. Solid-State Circuits*, vol. 27, no. 10, pp. 1470-1475, October 1992.

- [8] J. B. Hughes, I. C. Macbeth, D. M. Patullo, "New Switched-Current Integrator", Elec. Lett., vol 26, no. 11, pp. 694-696, 24th May 1990.

- [9] C. G. Montoro, M. C. Schneider and I. J. B. Loss, "Series-parallel association of FET's for high gain and high frequency applications", to appear in *IEEE J. Solid-State Circuits*, September 1994.

# ↑0.1 V/div

→50 µs/div

Fig.5 -Integrator ( $\beta$ =7/8) output and input waveforms measured at 3.6 kHz, the approximate -6dB frequency for a clock frequency of 100 kHz .

Fig.6 -Measured magnitude responses of the SI integrator for a clock frequency of 100 kHz.