# NONLINEARITIES OF CAPACITORS REALIZED BY MOSFET GATES

A.T.Behr, M.C.Schneider, S.Noceti Filho, and C.G.Montoro.

Laboratório de Instrumentação Eletrônica - LINSE/EEL/CTC/UFSC/C.P. 476

CEP 88049 - Florianópolis - SC - Brasil

Telex 240 UFSC BR Fax 55-0482-341524

Tel. 55-0482-319504/319643 e-mail: LINSE@BRUFSC.BITNET

Abstract: The capacitive gate structures available in digital oriented CMOS processes are reviewed, with emphasis on their use as linear capacitors. Experimental and analytical results indicate that the total harmonic distortion in an adequately biased (2.5V) gate capacitor can be kept low (THD < -40 dB for a 3V voltage swing ).

#### INTRODUCTION

For economical reasons, the analog part of a system-on-a-chip must be fully compatible with standard VLSI processes [1]. Most analog applications require high-quality capacitors, usually obtained through a nonconventional process, with the double-polysilicon option being the most frequently used.

One way to avoid the need for nonstandard processes to implement linear capacitors is through the use of the MOSFET gate structure, the intrinsic element of any MOS technology. Compared with double-poly capacitors, thin oxide capacitors present a larger capacitance per unit area and are expected to have better matching properties [2]. By properly biasing this device, a capacitor with weak nonlinearities is accomplished which is, however, much more voltage-dependent than the double-poly capacitor.

Some authors have described the use of gate capacitors in analog applications as, for example, in transconductance—C [3], transistor—only [4,5] and switched capacitor [6] filters. Despite the reported use of the gate structure in many analog applications, a more detailed analysis of this capacitor is necessary for the understanding of the impact of its use in practical filters.

The purpose of this paper is to evaluate the behavior of MOS gates as lumped capacitors. To this end, the capacitive structures available in CMOS technology are reviewed. An accurate model of the gate capacitance together with a numerical analysis and a design-oriented expression of the voltage harmonic distortion are presented. Finally, experimental data measured on an integrated capacitor are shown.

## GATE STRUCTURES IN CMOS TECHNOLOGY

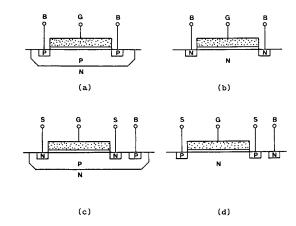

Fig. 1 shows 4 gate structures that can be employed as capacitors in a p-well CMOS process. The first two (1(a) and 1(b)) must operate in accumulation while the last two must be biased in strong inversion. The device in Fig. 1(a) can act as a floating capacitor. Fig. 1(b) shows an AC grounded capacitor. The device in Fig. 1(c) can be shielded from substrate noise by applying a fixed potential to the well, while the one shown in Fig. 1 (d) is a floating capacitor also available in a single channel technology.

Usually, some simple expressions are given for the intrinsic gate capacitance in strong inversion, for  $\rm V_{DS}^{=}\ 0$  :

$$C_{gs} = C_{gd} \cong \frac{1}{2} Cox; C_{gb} \cong 0$$

(1a)

Moreover, in accumulation:

$$C_{gs} = C_{gd} = 0$$

and  $C_{gb} = C_{ox}$  (1b)

where Cox is the thin oxide intrinsic capacitance. The other intrinsic capacitances,  $\rm C_{bs}$  and  $\rm C_{bd}$  , are nonlinear [7] and depend on  $\rm V_{RS}$  .

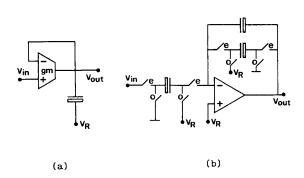

For the purpose of getting a nearly voltage-independent capacitance, a voltage bias must be provided to the MOS gate to keep it in accumulation or strong inversion. This is easy to realize for grounded and virtually grounded capacitors, as in the OTA-C and SC integrators shown in Fig. 2.

### ACCURATE MODEL OF THE GATE CAPACITANCE

Most analytical models of the MOSFET are based on the charge sheet approximation, in which the thickness of the surface channel (in inversion or accumulation) is neglected [7]. For these models the gate-to-source capacitance ( $\rm c_{\rm gs}$ ) is constant for  $\rm v_{\rm DS}$  = 0 . So, in order to calculate the weak nonlinear behavior of gate capacitors in inversion and accumulation, an approach based on fundamental equations of the MOS structure must be followed.

For the three terminal n-channel MOS structure, the voltage and electrical charge in terms of the surface potential  $(\psi_{\rm S})$  are given by the well-known expressions, valid for nondegenerate silicon [7]:

$$V_{GB} = V_{FB} + \psi_{S} - q_{C}^{\prime}/C_{OX}^{\prime}$$

(2)

$$q_c' = -sgn(\psi_s) (2q_{\varepsilon_s}N_A \theta_t)^{0.5}. f(\psi_s)$$

(3)

where

$$f(\psi_S) = \left\{ e^{-\frac{\psi_S}{\theta_t}} + \frac{\psi_S^{-(2\theta_F + V_{SB})}}{\theta_t} \right\}^{0.5}$$

${

m V}_{

m GB}$  is the gate-to-bulk voltage,  ${

m q}_{

m C}'$  is the total semiconductor charge per unit area and  ${

m C}_{

m OX}'$  is the oxide capacitance per unit area. The other variables have their usual meanings [7].

The total small signal gate capacitance per unit area is given by

$$C_{g}' = \frac{dq_{G}'}{dV_{GB}} = -\frac{dq_{C}'}{dV_{GB}}$$

(4)

where

$$C_g' = C_{gS}' + C_{gd}' + C_{gb}'$$

if  $V_{BS} = V_{DS} = 0$  .

As previously stated, the gate structure should be biased in strong inversion or accumulation in order to obtain a nearly voltage-independent capacitance. So, the voltage harmonic distortion in these two regions will be analitically determined for  $V_{\rm RS} = V_{\rm DS} = 0$ .

a)Strong inversion: For  $\psi_{\rm S} \geq 20^{\rm F}_{\rm F}$  the term e can be neglected in (3). From (2), (3) and (4), the value of C'\_g at a bias voltage V\_GB can be approximated by:

$$\frac{1}{C_{g}^{3}} \cong \frac{1}{C_{OX}^{3}} \left\{ 1 + \frac{20}{V_{FB} + \psi_{S} - V_{GB}} \right\}$$

(5)

In analog circuits the MOS capacitor is typically driven by a charge source, as in SC circuits, or by a current source, as in OTA-C networks. From expressions (2), (4), (5) and assuming  $\psi_{\rm S}$  constant, it can be shown that the second order harmonic distortion of the voltage, for a sinusoidal charge, is given by

2ND HARM DIST

$$\cong \frac{\theta_t \cdot V_p}{2(V_R - V_{FB} - \psi_s)^2}$$

(6)

where  $\rm V_R$  and  $\rm V_P$  are the bias and peak values of the gate-to-bulk voltage, respectively, and  $\rm V_R\cong 20_C$  .

b) Accumulation region: If  $\psi \le 0$  equations (5) and (6) still hold, with  $\psi_S \cong 0$ .

#### EXPERIMENTAL RESULTS

A test-capacitor, made up of 500 thin oxide unity capacitors of 40  $\mu m$  x 40  $\mu m$ , has been fabricated in a  $2\mu m$  CMOS n-well process. The main electrical parameters concerning the available CMOS process are a specific capacitance of 0.86 fF/ $\mu m^2$ , a well doping concentration of 1.9x10<sup>16</sup> cm<sup>-3</sup> and a threshold voltage of -0.6V for the PMOS transistor.

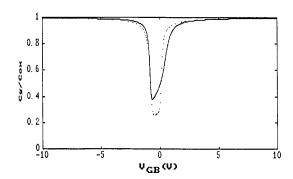

The experimental C-V characteristic of the test structure with source and well short-circuited, together with the theoretical C-V characteristic, are shown in Fig. 3. The latter was plotted from the data obtained by using expressions (2)-(4) and the typical values of process parameters referred to before. The difference between experimental and theoretical capacitance data in the depletion region (near the minimum of the capacitance curve) is explained by the nonuniform doping profile of the well

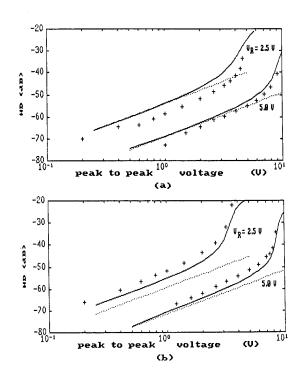

Fig. 4 displays the total harmonic distortion (THD) experimentally measured, its values computed from Fourier analysis based on expressions (2)-(3) and the second harmonic relative magnitude computed from equation (6). Spectral analysis has revealed that the second order harmonic is the main responsible for distortion. It should be noted that for a 2.5V bias, the peak to peak signal in the MOS gate can be about 4V (in accumulation) and the THD remains below -40 dB. For a 5V bias the peak to peak signal can be about 9V for achieving a THD close to -40 dB. Similar results also apply to the strong inversion region (Fig. 4 (b)).

### CONCLUSIONS

In spite of being a nonlinear element, the gate structure of the MOS transistor biased in inversion or accumulation provides a capacitance with the following advantages over double-poly capacitors: higher capacitance per unit area, better matching and full compatibility with any digital MOS process.

Harmonic distortion in gate capacitors is almost independent of technological parameters provided that they are biased in accumulation or strong inversion. Moreover, the approximate formula presented for the harmonic distortion can help the circuit designer predict a maximum voltage swing in order to maintain the THD at acceptable levels.

Analytical and experimental results have demonstrated that the THD can be lower than 1% for a voltage swing approximating the power supply voltage. Hence, for many applications, the harmonic distortion introduced by the weak nonlinearities of biased MOS gate capacitors can be kept low with little penalty in signal swing.

#### **ACKNOWLEDGEMENT**

The authors would like to thank F. Reichert from ELETROSUL for his help in measurements. They also acknowledge R. T. Gonçalves for devices characterization, Prof. A. Perin for his cooperation and Prof. J.C.M.Bermudez for valuable discussions.

#### REFERENCES

- [1] E. Vittoz, "The design of high-performance analog circuits on digital CMOS chips", IEEE J. Solid-State Circuits, Vol. SC-20, no.3, pp. 657-665, June 1985.

- [2] D.J. Allstot and W. Black, "Technological design considerations for monolithic MOS switched-capacitor filtering systems", Proc. of the IEEE, Vol. 71, no. 8, pp. 967-986, August 1983.

- [3] M.A. Tan , and R. Schaumann, "Simulating general-parameter LC-ladder filters for monolithic realizations with only transconductance and grounded capacitors", IEEE Trans. on Circuits and Systems, Vol. CAS-36, no. 2, pp. 299-307, February 1989.

- [4] L. Pu and Y. Tsividis, "Transistor-only frequency-selective circuits", IEEE J. Solid-State Circuits, Vol. SC-25, no. 3, pp. 821-832, December 1990.

- [5] S.T. Dupuie, S. Bibyk and M. Ismail, "A novel all-MOS high-speed continuous-time filter", Proc. of the International Symposium on Circuits and Systems, Portland, USA, pp. 675-678, 1989.

- [6] C.G. Montoro and J.C.M. Bermudez, Switched-capacitor circuits fully compatible with digital Si-gate single poly technology, Proc. of the 31st Midwest Symposium on Circuits and Systems, St. Louis, USA, pp. 1-3, 1988.

- [7] Y. Tsividis, Operation and modeling of the MOS transistor, New York, McGraw-Hill, 1987.

Fig. 1 - Gate structures in a p-well CMOS technology

Fig. 2 - Bias schemes for a lossy integrator. All capacitors have a DC operating point equal to V<sub>R</sub>

(a) OTA-C; (b) switched-capacitor [6].

Fig. 3 - C-V characteristic of the test-capacitor

theoretical

experimental

Fig.4 - Harmonic distortion for a measurement frequency of 2.5 KHz.

(a) accumulation (b) inversion theoretical expression (6) for the second harmonic

THD computed from expressions (2) and (3) experimental THD