## **Compact Modeling of Nonlinearities in Submicron MOSFETs**

P.D. da Silva\*, F.R. de Sousa\*\*, C.G. Montoro\* and M.C. Schneider\*

\*Federal University of Santa Catarina, Integrated Circuit Laboratory, 88040-900 – Florianópolis – SC – Brazil, pablo, Carlos, Marcio@eel.ufsc.br \*Federal University of Rio Grande do Norte, Electrical Engineering Department, Natal – RN – Brazil, frangel@dee.ufrn.br.

#### **ABSTRACT**

We propose in this work a compact model for  $3^{\rm rd}$  order nonlinearities in MOSFET transistors derived from the short-channel version of the Advanced Compact MOSFET (ACM) model equations. In addition we discuss the physical causes of the linearity improvement observed in moderate inversion. From our measurements we conclude that the  $2^{\rm nd}$  order effects related with mobility degradation are the main causes of the observed improvement in linearity.

*Keywords*: CMOS compact models, moderate inversion level, intermodulation distortion, nonlinearity, radio frequency (RF) integrated circuits.

#### 1 INTRODUCTION

CMOS technology is becoming a popular choice for RF circuit designers. Therefore, simple and reliable MOSFET models taking in account the most important aspects in RF circuit design are strongly desired. MOSFETs biased in weak inversion can drain little current from power supplies, however at the expense of deteriorating the linearity.

Some previous works [2][3][4] and our own measurement results have shown there is a peak of linearity in moderate inversion level which is a region where one can find a good trade off between low-power consumption, high transition frequency and high linearity. The referred linearity peak was named "sweet spot" in [2] and can be an interesting design criterion for low power RF CMOS circuits in which linearity is essential. Despite the verification of the "sweet spot" in the mentioned works, the physical effects which are related with this phenomenon have not been discussed.

The goal of this work is to show which physical effects related to the charge transport mechanisms are at the origin of the "sweet spot" and present simple and reliable equations for nonlinear analysis of MOSFET amplifiers, especially when they operate in weak and moderate inversion levels.

The paper is organized as follows: after this brief introduction, we show in section 2 a nonlinear analysis for a common-source (CS) amplifier using the power series expansion method. Which physical 2<sup>nd</sup> order effects are relevant in the nonlinearity model and the model

development itself are discussed in section 3. Finally, in section 4, measurements results and comparisons between it and the developed equations are presented.

## 2 CS-AMPLIFIER NONLINEAR ANALISYS

The study of  $3^{\rm rd}$  order nonlinearities are very important in RF circuit design due to the several undesired effects they introduce. The most accepted figure of merit used to evaluate  $3^{\rm rd}$  order nonlinearities is the  $3^{\rm rd}$  order intercept point (IP3). The IP3 is a theoretical point where the magnitude of the  $3^{\rm rd}$  order intermodulation products (IM3)  $(2\omega_1-\omega_2 \ \text{and} \ 2\omega_2-\omega_1)$  are equal to the magnitude of fundamental terms ( $\omega_1 \ \text{and} \ \omega_2$ ), when two sinusoidal tons of frequency  $\omega_1 \ \text{and} \ \omega_2$  are injected at the circuit input.

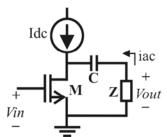

Figure 1 shows a CS amplifier which is the simplest amplifier topology widely used in analog and RF integrated circuits design.

Figure 1: Common Source Amplifier

The small signal analysis has been used to derive linear transfer functions of amplifiers and other circuits; however, it can be useful for finding nonlinear transfer functions as well. In order to avoid the dependence of the transfer function with the circuit load, we chose respectively the current and the voltage as the dependent and independent variables.

For the circuit shown at Figure 1, considering the MOSFET saturated and biased with a constant voltage at the drain, one can derive a general transfer function relating drain current and input voltage as:

$$id = \sum_{j=1}^{\infty} k_j vin^j \tag{1}$$

where  $k_i$  is given by:

$$k_{j} = \frac{1}{j!} \frac{\partial^{j} I dc}{\partial V i n^{j}} \tag{2}$$

Notice that for the circuit under analysis Vin=Vg , then  $k_j$  represent the gate transconductance ( gmg ) and its derivatives.

Notice that for the circuit under analysis the first derivative of Idc with respect to Vg is the definition of gmg, then its derivatives are gmg', gmg'' and so on. Replacing (2) and (1) in the original definition of  $V_{IP3}^2$  found in [1], we can rewrite  $V_{IP3}^2$  as:

$$V_{IP3}^{2} = 8 \frac{gmg}{gmg} = \frac{4}{3} \frac{\partial Idc}{\partial Vg} / \frac{1}{3!} \frac{\partial^{3} Idc}{\partial Vg^{3}}$$

(3)

As (3) is a general expression at circuit abstraction level and we are interested at the relationship between  $V_{lP3}^2$  and the bias voltage, we are supposed to include a model containing this relation. In this work the ACM [5] [6] model is used in all analysis except that when the opposite is said.

# 3. PROPOSED EQUATIONS FOR NONLINEARITIES

In this section, we investigate the physical effects related to the "sweet spot" in moderate inversion region. In addition, we derive a simple set of equations for helping RF designers to predict the 3<sup>rd</sup> order nonlinearities effects.

## 3.1. Using a Long-Channel Model

Although previous woks [2] [3] [4] have shown an interesting singularity in IP3 through measurements and predictions, they do not explain the physical origin of the phenomenon. In [2], a long-channel MOSFET model was used to calculate the transistor gate transconductance and its derivatives though the charge mobility and channel length were supposed to be constant. The relationship between drain current (Ids) and gate voltage (Vgs), used in [2] is rewriten in (4) for convenience, where n is the slope factor,  $\mu_0$  is the low field mobility, C ox is the oxide capacitance per unit area and  $\phi t$  is the thermal voltage.

$$I_{ds} = \left(2n\mu_0 C'_{ox} \phi t^2 \frac{W}{L}\right) \left[\ln\left(1 + e^{\frac{(Vgs - Vth)}{2n\phi t}}\right)\right]^2 \tag{4}$$

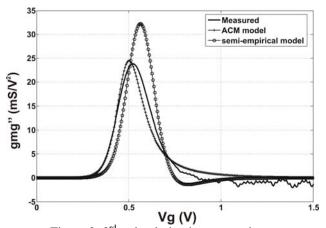

In order to confirm the need of the short-channel model for the "sweet spot" modeling in CMOS devices we made a comparison between the  $3^{\rm rd}$  derivative of Ids with respect to Vgs using (4), using ACM model long-channel approximation [5][6] and a measurements from of a  $16x1600 \ \mu m^2$  length AMIS 1.5  $\mu m$  transistor. The results are plotted in Figure 2, from which we notice that gmg' crosses zero for both the semiempirical model prediction and the measurement data, indicating the existence of the sweet spot. On the other hand, the gmg' predicted by the ACM equations do not show zero crossing or, in other words, the ACM long-channel model does not predict the sweet spot.

The long channel ACM model is strongly physics-based and it was proven to be very accurate for all inversion levels [6], which leads us to infer that the sweet spot must be related to second order effects, in particular, the charge mobility degradation due to transversal field.

Figure 2: 3<sup>rd</sup> order derivative comparison.

### **3.2.** Proposed Equations

The growing market of RF applications requires a deep shrink in transistor lengths in order to cope with the high transition frequency required by RF applications. As a consequence, RF designers must choose the most modern technologies, justifying studies focused on 2<sup>nd</sup> order (short-channel) effects.

In a first approximation was considered only the carrier velocity saturation effect because it is a main phenomenon related with short-channel devices. The carrier velocity saturation is related with the longitudinal electric field in the channel when the carrier velocity saturate instead of growing proportional with the electrical field. Usually this effect is modeled as mobility degradation in well-known MOSFET models as ACM [5].

In ACM model the channel is split in two parts when the velocity of the carries is saturated, one side is the source side where long-channel approximation is still valid and the drain side where the current is proportional to the charge density in the drain. In [5] was developed an equation for the charge density in drain side in relation with the charge density in the source side shown in equation(5).

$$\frac{q'_{DSAT}}{q'_{IS}} = 1 + \frac{\varepsilon + 1}{\varepsilon q'_{IS}} \left( 1 - \sqrt{1 + \frac{2\varepsilon q'_{IS}}{(\varepsilon + 1)^2}} \right)$$

(5)

Where  $q'_{DSAT}$  and  $q'_{IS}$  are the normalized charge densities in the drain and in the source respectively,  $\varepsilon = \phi t / \left( L_{eq} U_{CRIT} \right)$  and  $U_{CRIT} = v_{\lim} / \mu_0$  are the velocity saturation coefficient and the critical electrical field,  $v_{\lim}$  is the carrier's limit velocity and  $L_{eq}$  is the effective channel length. The normalization charge for the charge densities is  $Q'_{IP} = -nC'_{ox} \phi t$ .

The goal is to obtain the derivatives of the drain current in relation with the gate voltage, for the case of carrier velocity saturated ACM model give us a relationship reproduced here in (6) for convenience where  $IS = \mu_0 n C' ox\phi t^2 W/2L$ .

$$gmg = IS \frac{2}{\varepsilon} \frac{\partial q'_{DSAT}}{\partial V_G} \tag{6}$$

Notice that (6) contains a derivative of (5), then it probably will result in a complex equation due to the square root in (5). To avoid a complex result we multiplied and divided (5) by it own conjugate resulting on the equation below:

$$\frac{q'_{DSAT}}{q'^{IS}} = \frac{2\varepsilon \left(1 + \frac{q'^{IS}}{2}\right)}{1 + \varepsilon \left(q'^{IS} + 1\right) + \sqrt{1 + 2\varepsilon \left(q'^{IS} + 1\right) + \varepsilon^2}}$$

(7)

Remembering that in the most used technologies  $\mathcal{E} \ll 1$ , we can simplify (7) without compromising the accuracy in weak and moderate inversion levels:

$$\frac{q'_{DSAT}}{q'_{IS}} = \frac{2\varepsilon \left(1 + \frac{q'_{IS}}{2}\right)}{2 + \varepsilon \left(q'_{IS} + 1\right)}$$

(8)

Equation (8) offers the possibility of a very simple equation for gmg and its derivatives as can be seen in (9) and (10) bellow.

$$gmg = \frac{2IS}{n\phi t} \frac{q'_{IS}}{2 + \varepsilon q'_{IS}} \left[ \frac{4 + \varepsilon q'_{IS}}{2 + \varepsilon q'_{IS}} \right]$$

(9)

$$gmg'' = \frac{16IS}{\left(n\phi t\right)^3} \frac{q' s}{\left(q' s + 1\right)^3} \frac{2 - 2\varepsilon q' s - 3\varepsilon q' s^2}{\left(2 + \varepsilon q' s\right)^4} \quad (10)$$

Notice that one of the roots of the quadratic equation in numerator of (10) represents the bias point where the "sweet spot" is located.

#### 4. MEASUREMENT RESULTS

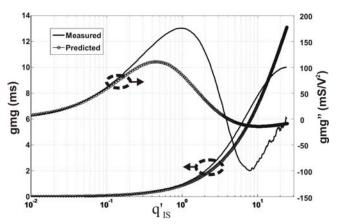

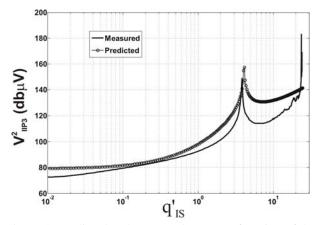

A straightforward method to obtain the  $V_{IIP3}^2$ , gmg and its derivatives is through the measurement of DC characteristics [3] ( $I_{dc} \times Vg$  curves). These curves were obtained using a high precision semiconductor analyzer Agilent 4156C. Then the transconductance and its derivatives were obtained by numerical differentiation. The measurements were made with a  $W(20\mu m)/L(0.2\mu m)$  transistor of the TSMC 0.18  $\mu m$  process.

The results obtained are shown in Figure 3 and Figure 4 and what one can observe is that, with the consideration of the carrier velocity saturation is possible obtain a simple equation with a good accuracy related to the "sweet spot", however it does not predict with accuracy the behavior of the transconductance in whole inversion level range. Figure 3 shows a necessity for addition of more second order effects, for instance, mobility degradation due to the transversal field.

Figure 3: Predicted and measured gmg and gmg" for a  $W(20\mu m)/L(0.2\mu m)$  transistor in the TSMC 0.18 process.

Figure 4: Predicted and measured  $V_{IP3}^2$  as a function of the normalized charge density in the source

Figure 4 shows the  $V_{IIP3}^2$  for a considerable range of inversion levels. Notice that there is a rise in linearity called "sweet spot" [2] and that is possible to predict with good accuracy using a simple equation the position of this point.

#### 5. CONCLUSION

The comparisons made between experimental results and the compact model presented show that the second-order effects, in especial those that cause degradation in carrier mobility, run as a potential cause to the "sweet spot". The effect of carrier mobility degradation in the gate transconductance is to saturate it. In addition, for models which any second-order effect are not taken into account the "sweet spot" should not show up as can be verified with the ACM model [5] [6].

A simple model considering only the carrier velocity saturation was presented and shown a good approximation for the "sweet spot" position, however not for to represent with accuracy the transconductance behavior in whole range of inversion level. The experimental result for a long-channel transistor show that the mobility degradation due to transversal field is an important effect to be considered, remembering that for long-channel transistor the velocity saturation is not taken in account.

## **REFERENCES**

- [1] Behzad Razavi, "RF Microelectronics", Prentice Hall communications engineering and emerging technologies series, 1998.

- [2] B. Toole, C. Plett and M. Cloutier, "RF Circuit Implications of Moderate Inversion Enhanced Linear Region in MOSFETs", IEEE Transactions on Circuits and Systems – I, vol 51, pp 319 – 328, February 2004.

- [3] P. H. Woerlee, M. J. Knitel, R. van Langevelde, D. B. M. Klaassen, L. F. Tiemeijer, A. J. Scholten and A. T. A. Zegers-van Duijnhoven, "RF-CMOS Performance Trends", IEEE Transactions on

- Electron Devices, vol 48, pp 1776 1782, August, 2001.

- [4] J. Ramos, A. Mercha, W. Jeamsaksiri, D. Jenei, R. Rooyackers, R. Verbeeck, S. Thijs, A. J. Scholten, P. Wambacq and I. Debusschere, S. Decoutere, "90nm RF CMOS Technology for low-power 900 MHz applications", ESSDERC 2004, pp 329 332, Proceeding of the 34<sup>th</sup> European 21-23 Sept. 2004.

- [5] C. Galup-Montoro, M. C. Schneider and A. I. A. Cunha, "A Current-Based MOSFET Model for Integrated Circuit Design", Chapter 2 in Low-Voltage/Low-Power Integrated Circuits and System, edited by E. Sanchez-Sinencio and A. G. Andreou, IEEE Press, August, 1998.

- [6] C. Galup-Montoro, M. C. Schneider and V. C. Pahin, 'Fundamentals of Next Generation Compact MOSFET Models", 18<sup>th</sup> Symposium on Integrated Circuits ansd Systems Design (SBCCI) 2005, Florianópolis, Brazil, pp 32 37, September 2005.

- [7] A. A. Maceira, "Very Large Constant Gm-C Filters", Universidade de la República, Uruguay, April, 2005.