## Simulação de Monte Carlo para Mismatch usando o Virtuoso

**Atenção:** o método para simulação apresentado a seguir foi aplicado e testado no contexto de um projeto de sinais mistos, com o uso da *view config* para permitir o uso do simulador *AMS*, em vez do *Spectre*. Para projetos que não seguem essas configurações, os demais passos e considerações devem ser similares, mas cabe atenção quanto a possíveis modificações.

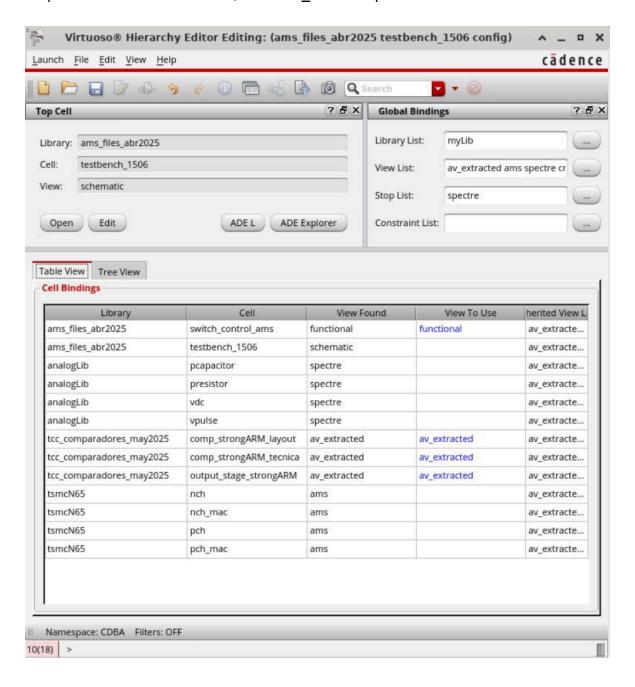

1. Após finalizar o esquemático do circuito de interesse e seu respectivo testbench, configure o arquivo config com as views que devem ser consideradas na simulação. Caso o leiaute para algumas partes do circuito ainda não tenha sido realizado, mantém-se a view schematic. Já caso o leiaute exista e a extração de parasitas tiver sido realizada, a view av\_extracted pode ser selecionada.

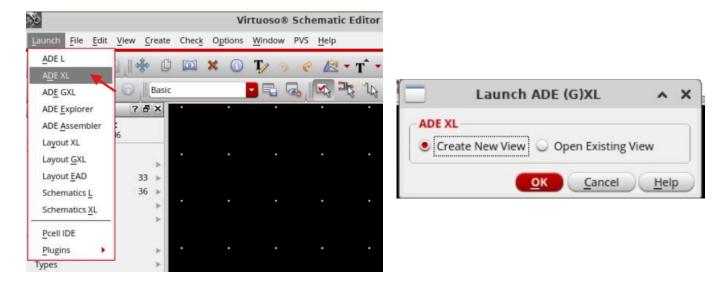

2. Em seguida, crie uma view ADE XL, onde será configurada a simulação de Monte Carlo.

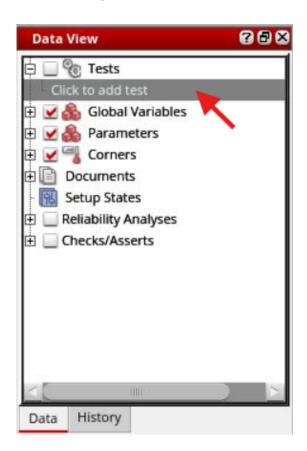

3. No ADE XL, as configurações a serem realizadas serão majoritariamente feitas na janela "Data View". Primeiramente, a simulação a ser executada deve ser configurada. Para isso, adiciona-se um **teste** conforme a figura abaixo.

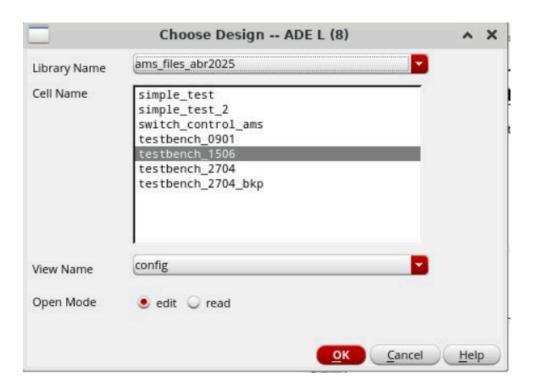

4. O teste a ser criado deve ser relativo a uma view específica. No caso do projeto utilizado como exemplo em que a view config já estava sendo aplicada, essa mesma view será utilizada como referência.

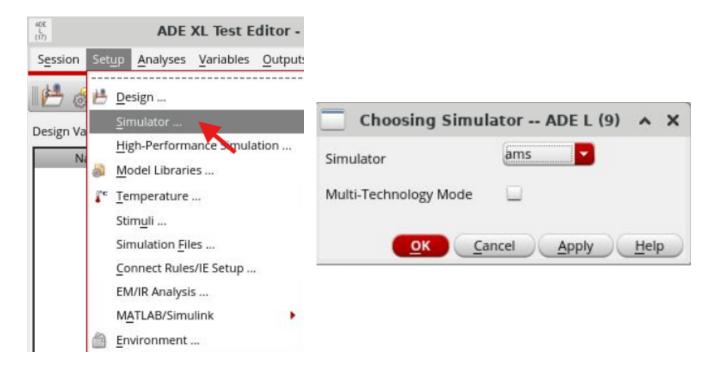

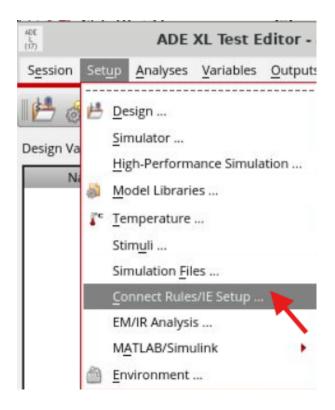

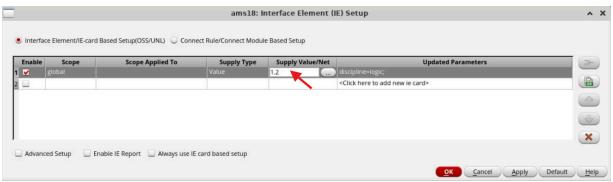

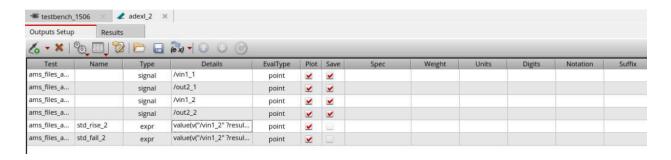

4.1 Após criar o teste, uma janela do ADE L será aberta e algumas configurações podem ser realizadas. Neste tutorial, adicionalmente, são apresentadas a escolha do simulador AMS e a modificação da tensão interpretada como nível lógico alto para a tecnologia. Essas modificações não são mandatórias para todos os casos, mas podem ajudar em algumas ocasiões.

5. Após criar o teste, adicione as saídas à simulação de interesse. Ao adicionar as saídas no ADE L, elas automaticamente aparecerão na janela geral do ADE XL. Caso seja pertinente para o projeto, é possível adicionar expressões (expr) no ADE XL, usando funções da calculadora que são aplicadas nas saídas escolhidas.

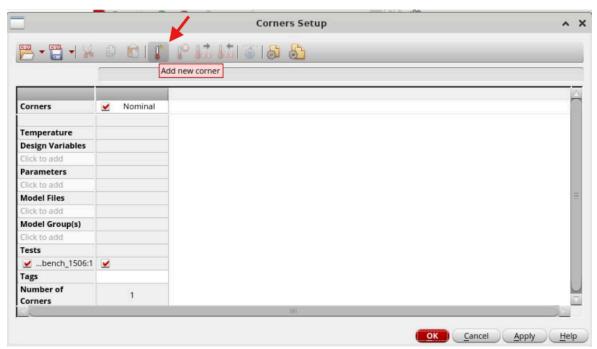

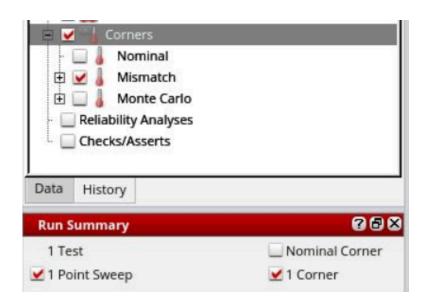

6. Após definir as saídas, configure os corners de interesse para a simulação. Apesar de ser possível adicionar múltiplos corners, eles serão utilizados separadamente na simulação. Por exemplo: para uma rodada de Monte Carlo com 100 amostras e 2 corners, serão executadas 200 amostras ao total, 100 para o primeiro corner e 100 para o segundo. Para adicionar um corner, selecione a respectiva opção no "Data View", conforme a figura abaixo.

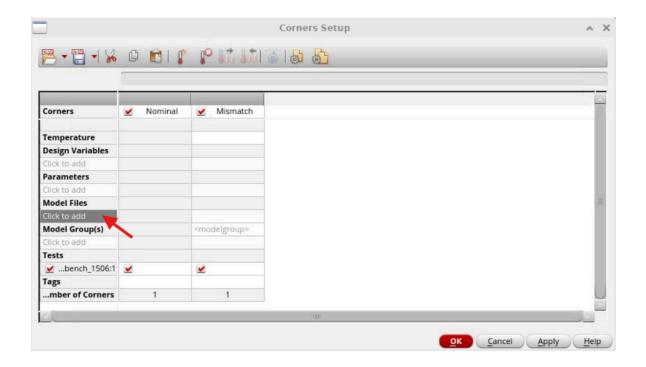

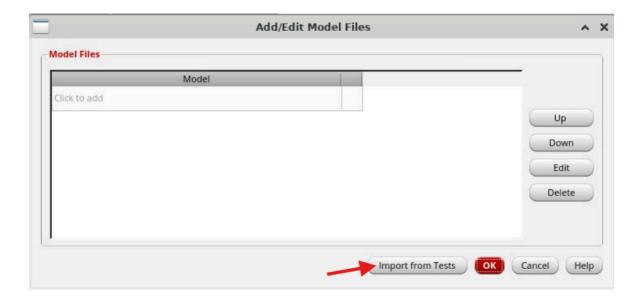

6.1. Neste tutorial, estaremos adicionando o corner relativo ao modelo de Mismatch. Para isso, clique em adicionar arquivos de modelo e então importe os modelos com base nos testes (botões Import from Tests + OK). Automaticamente, os modelos disponíveis serão carregados para a janela "Add/Edit Model Files" e será possível escolher entre as opções disponíveis na janela "Corners Setup".

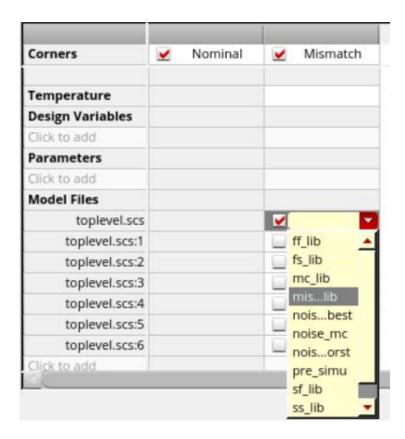

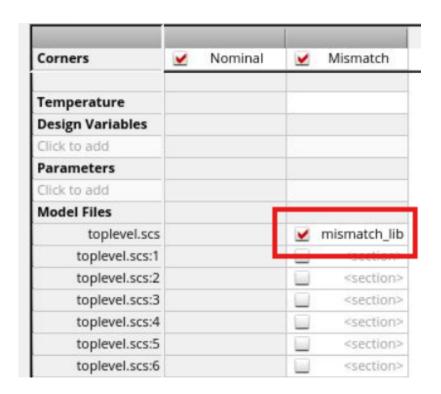

6.2 Selecione o modelo "mismatch\_lib" na tela "Corners Setup" com base no Model Files "toplevel.scs", conforme mostram as figuras a seguir.

6.3. Abrindo o arquivo toplevel.scs, é possível entender porque o modelo "mismatch\_lib" precisa ser considerado para que existam variações entre os componentes em uma mesma amostra (mismatch) e não somente variação de processo entre amostras. Apenas para "mismatch\_lib" as mismatch flags dos transistores e demais dispositivos estão habilitadas.

```

section mc lib

include "crn65lp 2d5 lk v1d7.scs" section=mc rfmos

include "crn65lp 2d5 lk v1d7.scs" section=mc rfmos hvt

include "crn65lp 2d5 lk v1d7.scs" section=mc rfmos mlvt

include "crn65lp_2d5_lk_v1d7.scs" section=mc_rfmos_lvt

include "crn65lp_2d5_lk_v1d7.scs" section=mc_rfmos_lvt

include "crn65lp_2d5_lk_v1d7.scs" section=mc_rfmos_18

include "crn65lp_2d5_lk_v1d7.scs" section=mc_rfmos_25ud18

include "crn65lp_2d5_lk_v1d7.scs" section=mc_rfmos_25

include "crn65lp_2d5_lk_v1d7.scs" section=mc_rfmos_25od33

include "crn65lp_2d5_lk_v1d7.scs" section=mc_rfmos_33

include "crn65lp 2d5 lk vld7.scs" section=mc_rfmim

include "crn65lp 2d5 lk v1d7.scs" section=mc rfmvar

include "crn65lp 2d5 lk v1d7.scs" section=mc rfmvar hvt

include "crn65lp 2d5 lk v1d7.scs" section=mc rfmvar 25

include "crn65lp 2d5 lk v1d7.scs" section=mc rfsbd

parameters mismatchflag mos hvt=0

parameters mismatchflag mos mlvt=0

parameters mismatchflag mos lvt=0

parameters mismatchflag mos 18=0

parameters mismatchflag mos 25=0

parameters mismatchflag mos 33=0

parameters mismatchflag mos 25ud18=0

parameters mismatchflag mos 25od33=0

parameters mismatchflag mos na=0

parameters mismatchflag mos na25=0

parameters mismatchflag mos hv25 snw spw=0

parameters mismatchflag bip=0

parameters mismatchflag bip npn=0

parameters mismatchflag bip s=0

parameters mismatchflag bip npn s=0

parameters mismatchflag cap=0

parameters mismatchflag cap 25=0

parameters mismatchflag res=0

parameters mismatchflag disres=0

parameters mismatchflag mim=0

parameters mismatchflag rtmom=0

endsection mc lib

```

```

section mismatch lib

include "crnb5lp 2d5 lk vld7.scs" section=tt rfmos

include "crn65lp_2d5_lk_v1d7.scs" section=tt_rfmos_hvt

include "crn65lp_2d5_lk_v1d7.scs" section=tt_rfmos_mlvt

include "crn65lp_2d5_lk_v1d7.scs" section=tt_rfmos_lvt

include "crn65lp 2d5 lk v1d7.scs" section=tt rfmos 18

include "crn65lp 2d5 lk v1d7.scs" section=tt rfmos 25ud18

include "crn65lp 2d5 lk v1d7.scs" section=tt rfmos 25

include "crn65lp 2d5 lk v1d7.scs" section=tt rfmos 25od33

include "crn65lp 2d5 lk vld7.scs" section=tt rfmos 33

include "crn65lp 2d5 lk v1d7.scs" section=tt rfmim

include "crn65lp 2d5 lk v1d7.scs" section=tt rfmvar

parameters mismatchflag mos 33=1

parameters mismatchflag mos 25ud18=1

parameters mismatchflag mos 25od33=1

parameters mismatchflag mos na=1

parameters mismatchflag mos na25=1

parameters mismatchflag mos hv25 snw spw=1

parameters mismatchflag bip=1

parameters mismatchflag bip npn=1

parameters mismatchflag bip s=1

parameters mismatchflag bip npn s=1

parameters mismatchflag cap=1

parameters mismatchflag_cap_25=1

parameters mismatchflag res=1

parameters mismatchflag disres=1

parameters mismatchflag mim=1

parameters mismatchflag rtmom=1

endsection mismatch lib

```

7. Para a simulação, o *corner "Nominal"* pode ser desabilitado, mantendo somente um *corner* relativo à "*mismatch lib"*.

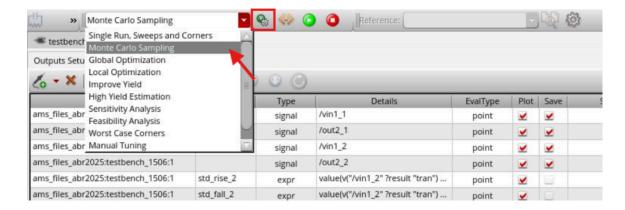

8. Selecione a opção "Monte Carlo Sampling" na janela do ADE XL, e então o ícone em destaque na imagem a seguir para configurar as informações relativas à sua simulação.

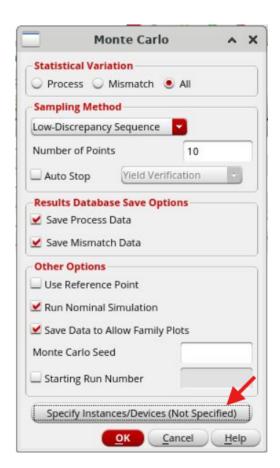

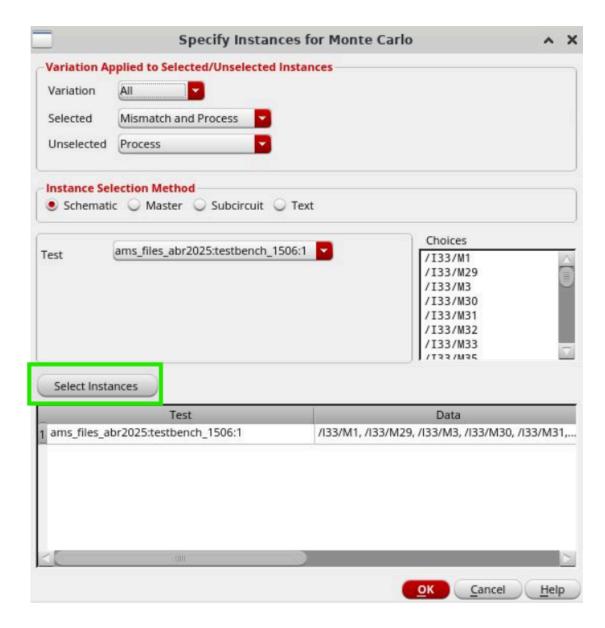

8.1. Nas configurações do presente exemplo, foram escolhidas as variações estatísticas tanto de *Mismatch* (variação dos parâmetros entre os dispositivos dentro de uma mesma amostra) quanto de Processo (variações dos dispositivos entre amostras). As demais opções dependem dos objetivos do usuário. Por fim, clique em "Specify Instances/Devices" para selecionar os dispositivos que devem sofrer variações.

**IMPORTANTE:** Os transistores convencionais devem estar com os modelos "\_mac", aptos para receberem as variações. Essa mudança pode ser feita de forma simplificada pela interface para alguns PDKs, alterando todos os transistores ao mesmo tempo por meio da janela de comandos do Virtuoso®.

8.3. Clique em "Select Instances" e então selecione manualmente os dispositivos a serem variados. Para descer um nível de hierarquia (passando do símbolo no *testbench* para o esquemático, por exemplo) use "Shift + E". Quando finalizar a seleção, pressione "ESC" e então "OK" na tela abaixo.

9. Por fim, na tela principal do ADE XL, selecione o ícone "Play" para dar início à simulação anteriormente configurada. Em algum tempo, seus resultados estarão disponíveis para serem analisados.

Fim do tutorial.