## RAFAEL LUCIANO RADIN

# MODELAGEM DA TENSÃO DE EARLY EM TRANSISTORES MOS NOS REGIMES DE INVERSÃO FRACA E MODERADA

FLORIANÓPOLIS 2007

# UNIVERSIDADE FEDERAL DE SANTA CATARINA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

# MODELAGEM DA TENSÃO DE EARLY EM TRANSISTORES MOS NOS REGIMES DE INVERSÃO FRACA E MODERADA

Dissertação submetida à

Universidade Federal de Santa Catarina

como parte dos requisitos para a

obtenção do grau de Mestre em Engenharia Elétrica.

## RAFAEL LUCIANO RADIN

Florianópolis, Novembro de 2007.

# MODELAGEM DA TENSÃO DE EARLY EM TRANSISTORES MOS NOS REGIMES DE INVERSÃO FRACA E MODERADA

### Rafael Luciano Radin

'Esta Dissertação foi julgada adequada para obtenção do Título de Mestre em Engenharia Elétrica, Área de Concentração em *Circuitos e Sistemas Integrados*, e aprovada em sua forma final pelo Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Santa Catarina.'

|                    | Prof. Márcio Cherem Schneider, D.Sc.<br>Orientador | -             |

|--------------------|----------------------------------------------------|---------------|

|                    | Prof <sup>a</sup> . Kátia Campos de Almeida, Ph.D. | -             |

| Coordenado         | ora do Programa de Pós-Graduação em Engenh         | aria Elétrica |

| Banca Examinadora: |                                                    |               |

|                    | Prof. Márcio Cherem Schneider, D.Sc.<br>Presidente | -             |

|                    | Ana Isabela Araújo Cunha, Dr.                      | -             |

|                    | Carlo Requião da Cunha, Ph.D.                      | -             |

|                    | Carlos Galup-Montoro, Dr.                          | -             |

### **AGRADECIMENTOS**

Agradeço a todas as pessoas que foram fundamentais para a realização deste trabalho: minha família, amigos, colegas e professores que estiveram presentes nesta importante etapa de minha formação.

Em especial gostaria de agradecer aos meus pais e a minha namorada Michely por seu amor e dedicação.

Agradeço o apoio do bolsista Gustavo Leão Moreira, pois sua ajuda na parte experimental foi fundamental para o bom andamento deste trabalho, e também meu orientador Márcio Cherem Schneider, por todo seu empenho e dedicação, sempre presente para esclarecer qualquer dúvida ou conceito.

Resumo da Dissertação apresentada à UFSC como parte dos requisitos necessários para a obtenção do grau de Mestre em Engenharia Elétrica.

# MODELAGEM DA TENSÃO DE EARLY EM TRANSISTORES MOS NOS REGIMES DE INVERSÃO FRACA E MODERADA

#### Rafael Luciano Radin

Novembro/2007

Orientador: Márcio Cherem Schneider, Dr. Eng.

Área de Concentração: Circuitos e Sistemas Integrados.

Palavras-chave: Modelagem do transistor MOS, Tensão de Early, Condutância de saída

Número de Páginas: 64

#### **RESUMO**

Este trabalho apresenta um modelo compacto para a tensão de Early do transistor MOS em inversão fraca e moderada. Utilizando as equações do modelo ACM (Advanced Compact Mosfet Model) e incluindo os efeitos de canal curto relevantes como o DIBL e a modulação do comprimento das zonas de depleção de dreno e fonte, chega-se a um modelo compacto para a tensão de Early que proporciona aproximações úteis para o projetista de circuitos integrados. Para extração de parâmetros do modelo proposto foram feitas medidas experimentais em transistores de diversos comprimentos, níveis de inversão e tensões de dreno. As curvas traçadas de acordo com o modelo compacto e com parâmetros extraídos para dispositivos em tecnologia CMOS 0,35 µm são comparadas às curvas experimentais. Os resultados obtidos comprovam a eficiência do modelo como uma aproximação para cálculos de primeira ordem.

i

Abstract of Dissertation presented to UFSC as a partial fulfillment of the requirements for the degree of Master in Electrical Engineering.

## MOS TRANSISTOR EARLY VOLTAGE MODELING IN WEAK AND MODERATE INVERSION

#### Rafael Luciano Radin

November/2007

Advisor: Márcio Cherem Schneider, Dr. Eng.

Area of Concentration: Integrated Circuits and Systems

Keywords: MOS Modeling; Early Voltage; Output Conductance.

Number of Pages: 64

#### **ABSTRACT**

This work presents a MOS transistor Early Voltage Model in weak and moderate inversion. Using the long channel ACM (Advanced Compact Mosfet Model) equations and including the short-channel effects that are relevant in these inversion regimes, like DIBL and length modulation of the source and drain depletion zones, an Early Voltage compact model with very helpful approximations for the integrated circuit designer is developed. In order to extract the model parameters, experimental measurements in transistors of different lengths, inversion levels and drain voltages were performed. The curves simulated with respect to the compact model using the CMOS 0.35mm parameters were compared with the experimental curves. The obtained results prove the model efficiency for first order approximations.

ii

# **SUMÁRIO**

| RESUMO                                                                          | i   |

|---------------------------------------------------------------------------------|-----|

| ABSTRACT                                                                        | ii  |

| SUMÁRIO                                                                         | iii |

| LISTA DE FIGURAS                                                                | iv  |

| LISTA DE ABREVIAÇÕES                                                            | vi  |

| LISTA DE SIMBOLOS                                                               | vii |

| LISTA DE TABELAS                                                                | ix  |

| 1. Introdução                                                                   | 1   |

| 2. O transistor canal longo                                                     | 3   |

| 3. Efeitos de canal curto                                                       | 7   |

| 3.1 DIBL                                                                        |     |

| 3.2 Zonas de depleção                                                           |     |

| 3.3 Avalanche fraca [23],[24],[25]                                              | 16  |

| 4. Tensão de early                                                              | 19  |

| 4.1 Definição de V <sub>A</sub>                                                 | 19  |

| 4.2 Cálculo de VA                                                               | 20  |

| 4.2.1 V <sub>ADIBL</sub>                                                        |     |

| 4.2.2 V <sub>ACLM</sub>                                                         | 22  |

| 4.2.3 V <sub>AWA</sub>                                                          |     |

| 5. Extração de parâmetros e resultados experimentais                            |     |

| 5.1 Extração de I <sub>S</sub>                                                  |     |

| 5.2 Curvas experimentais                                                        | 26  |

| 5.2.1 Características de saída experimentais - I <sub>D</sub> x V <sub>DS</sub> | 27  |

| 5.2.2 Condutância de saída experimental - $g_{ds}$ x $V_{DS}$                   |     |

| 5.2.3 Tensão de Early experimental - $V_A \times V_{DS}$                        |     |

| 5.3 Extração do parâmetro do DIBL                                               |     |

| 5.4 Simulação e ajuste de parâmetros                                            |     |

| 6. Conclusão                                                                    | 51  |

| 6.1 Trabalhos futuros                                                           |     |

| Apêndice A – Cálculo do comprimento da zona de depleção de dreno                |     |

| Apêndice B – Metodologia de extração de I <sub>S</sub>                          |     |

| Apêndice C – Dedução da equação (5.3.3)                                         |     |

| REFERÊNCIAS BIBLIOGRÁFICAS                                                      | 61  |

# LISTA DE FIGURAS

| Figura 2.1- Estrutura simplificada do transistor MOS 4 terminais3                                                   |

|---------------------------------------------------------------------------------------------------------------------|

| Figura 3.1 – Variação do potencial de superfície ao longo do canal (transistor canal longo e                        |

| curto)9                                                                                                             |

| Figura 3.2 – Zonas de depleção nas junções de transistores MOS                                                      |

| Figura 3.3 – Distribuição de cargas em um transistor MOS em saturação                                               |

| Figura 3.4 – Perfil do campo elétrico ao longo do canal                                                             |

| Figura 3.5 – Ionização através de impacto                                                                           |

| Figura 5.1 – Conexão elétrica para extração da curva $I_D x V_{DS}$ (transistores canal N) 27                       |

| Figura 5.2 – $I_D$ x $V_{DS}$ (TSMC 0,18 $\mu$ m) - (a) transistor $T_1$ (L=Lmin) - (b) transistor $T_2$            |

| $(L=2Lmin)$ - (c) transistor $T_3$ ( $L=4Lmin$ ) - (d) transistor $T_4$ ( $L=8Lmin$ )                               |

| Figura 5.3 – $I_D \times V_{DS}$ (TSMC 0,35µm canal N) - (a) transistor $T_1$ (L=Lmin) - (b) transistor             |

| $T_2$ (L=2Lmin) - (c) transistor $T_3$ (L=4Lmin) - (d) transistor $T_4$ (L=8Lmin)29                                 |

| Figura 5.4 – Detalhe da corrente do transistor T <sub>2</sub>                                                       |

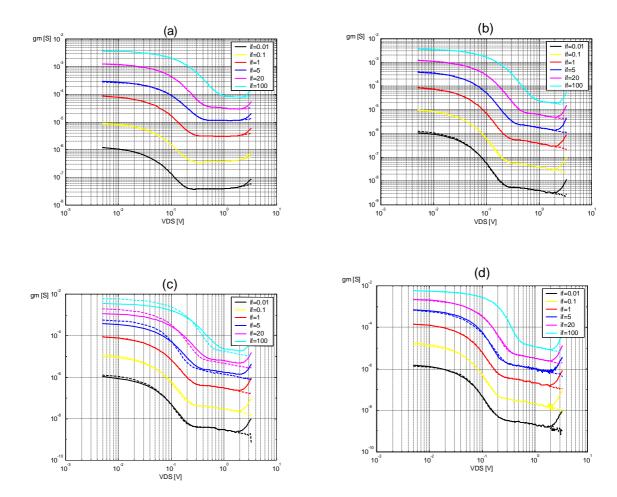

| Figura 5.5 – $g_{ds} \times V_{DS}$ (TSMC 0,18µm) - (a) transistor $T_1$ - (b) transistor $T_2$ - (c) transistor    |

| T3 - (d) transistor T <sub>4</sub>                                                                                  |

| Figura 5.6 – $g_{ds} \times V_{DS}$ (TSMC 0,35 $\mu$ m canal N) - (a) transistor $T_1$ - (b) transistor $T_2$ - (c) |

| transistor $T_3$ - (d) transistor $T_4$                                                                             |

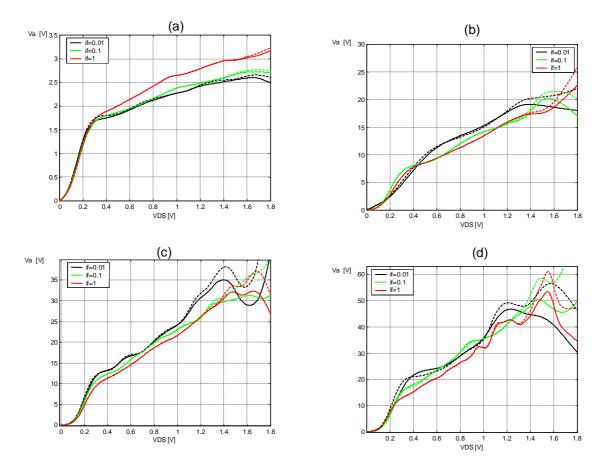

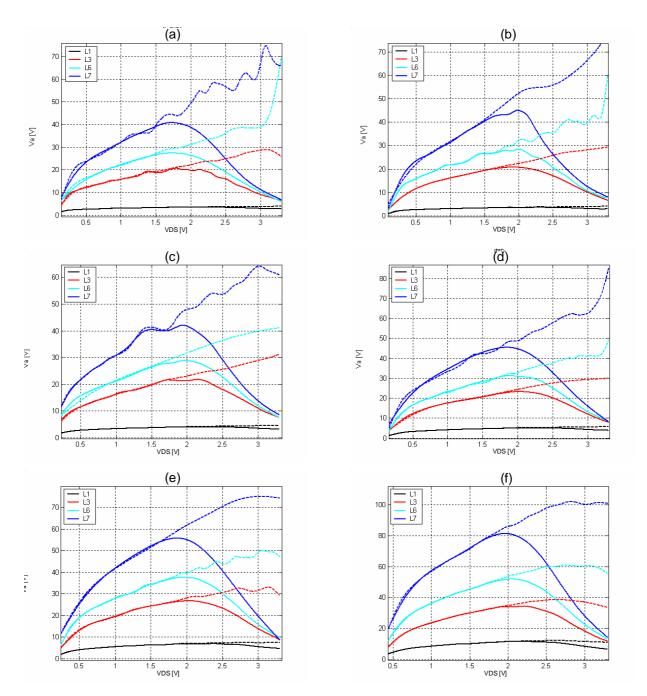

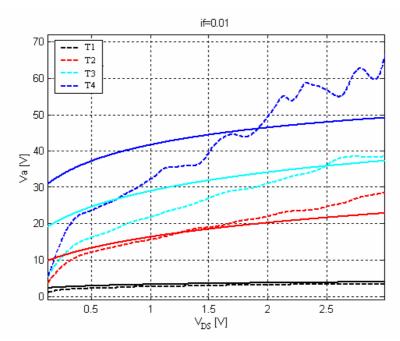

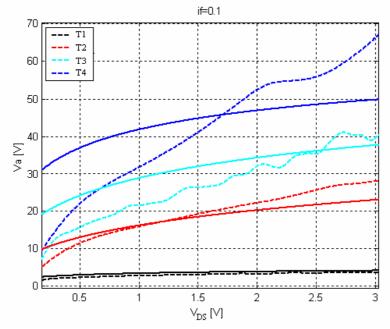

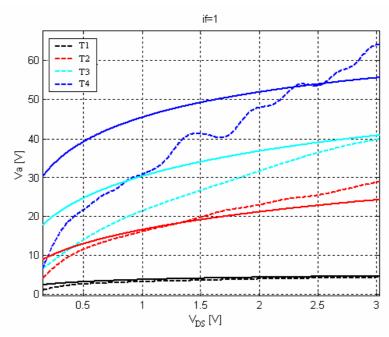

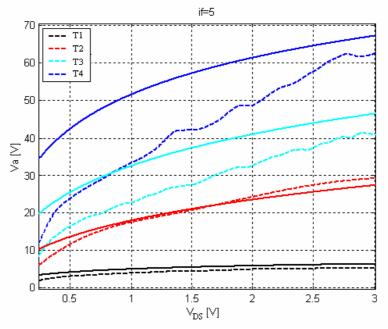

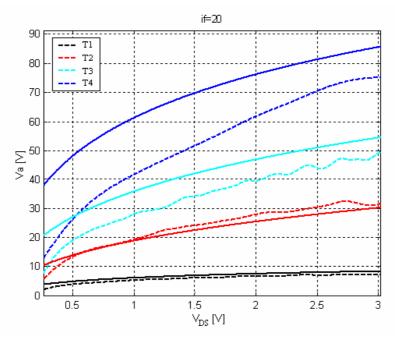

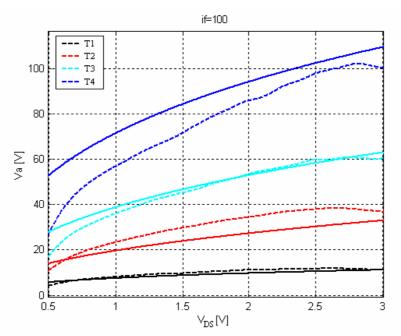

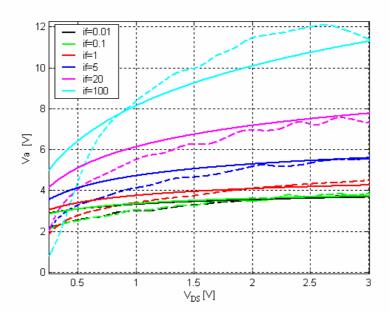

| Figura 5.7 – $V_A$ x $V_{DS}$ (TSMC 0,18µm) - Comprimento fixo para vários $i_f$ 's - (a) transistor                |

| $T_1$ - (b) transistor $T_2$ - (c) transistor $T_3$ - (d) transistor $T_4$                                          |

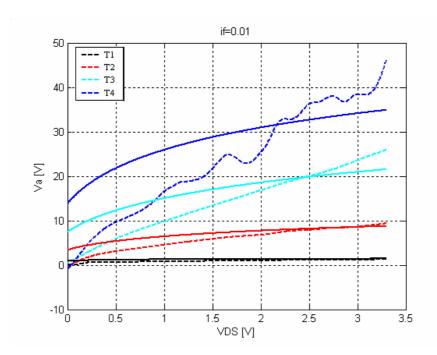

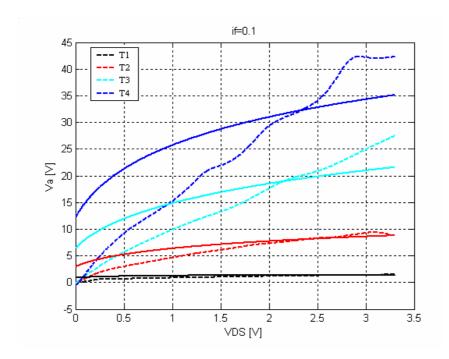

| Figura 5.8 – $V_A \times V_{DS}$ (TSMC 0,18µm) - $i_f$ fixo para vários comprimentos de canal - (a)                 |

| $i_f$ =0,01 - (b) $i_f$ =0,1 - (c) $i_f$ =134                                                                       |

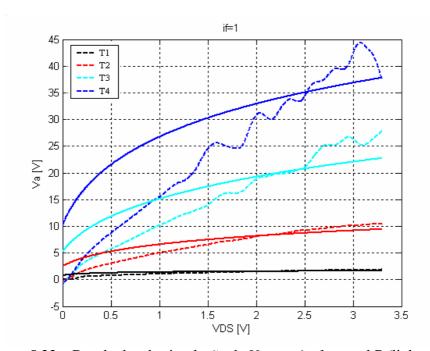

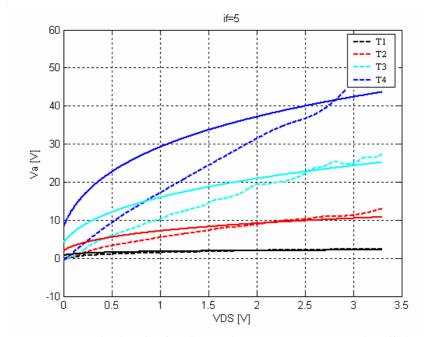

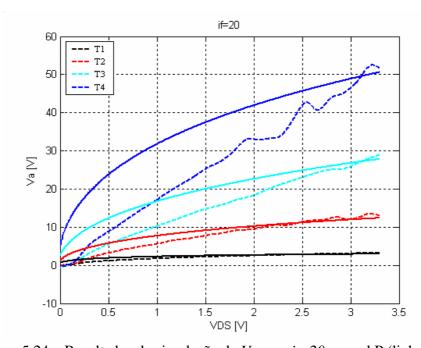

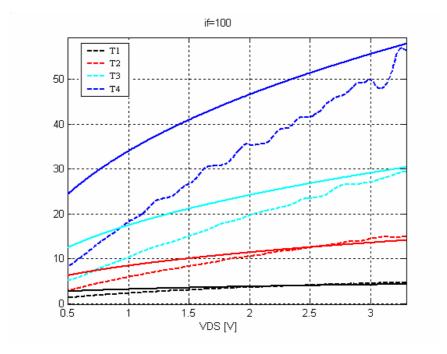

| Figura 5.9 – $V_A \times V_{DS}$ (TSMC 0,35µm canal N) - Comprimento fixo para vários $i_f$ 's - (a)                |

| transistor $T_1$ - (b) transistor $T_2$ - (c) transistor $T_3$ - (d) transistor $T_4$                               |

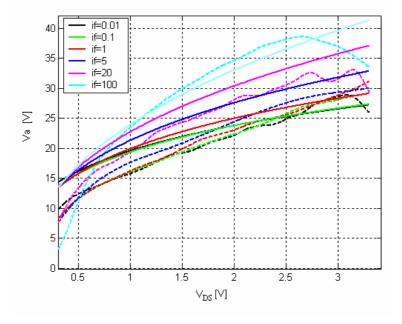

| Figura 5.10 – $V_A \times V_{DS}$ (TSMC 0,35µm canal N) - $i_f$ fixo para vários comprimentos de canal              |

| - (a) $i_f$ =0,01 - (b) $i_f$ =0,1 - (c) $i_f$ =1 (d) $i_f$ =5 - (e) $i_f$ =20 - (f) $i_f$ =100                     |

| Figura 5.11 – $V_A \times V_{DS}$ (TSMC 0,35µm canal P) - $i_f$ fixo para vários comprimentos de canal              |

| - (a) $i_f$ =0,01 - (b) $i_f$ =0,1 - (c) $i_f$ =1 (d) $i_f$ =5 - (e) $i_f$ =20 - (f) $i_f$ =10037                   |

| Figura 5.12 – Extração do parâmetro do DIBL                                                                         |

| Figura $5.13 - I_D \times V_S$ para um transistor de canal longo (tracejado) e um de canal curto                    |

| (contínuo)39                                                                                                        |

| Figura 5.14 – Resultados de simulação de $V_A$ para $i_f$ =0,01 - canal N (linhas contínuas-                        |

| modelo/ linhas tracejadas- experimentais)                                                                           |

| Figura 5.15 – Resultados de simulação de $V_A$ para $i_f$ =0,1 - canal N (linhas contínuas-                         |

| modelo/ linhas tracejadas- experimentais)                                                                           |

| Figura 5.16 – Resultados de simulação de $V_A$ para $i_f=1$ - canal N (linhas contínuas- modelo/                    |

| linhas tracejadas- experimentais)                                                                                   |

| Figura $5.17$ – Resultados de simulação de $V_A$ para $i_f$ = $5$ - canal N (linhas contínuas- modelo/              |

| linhas tracejadas- experimentais)                                                                                   |

| Figura $5.18$ - Resultados de simulação de $V_A$ para $i_f$ =20 - canal N (linhas contínuas-                        |

| modelo/ linhas tracejadas- experimentais)45                                                                         |

| Figura 5.19 – Resultados de simulação de $V_A$ para $i_f$ =100 - canal N (linhas contínuas-                         |

| modelo/ linhas tracejadas- experimentais)45                                                                         |

| Figura 5.20 – Resultados de simulação de $V_A$ para $i_f$ =0,01 - canal P (linhas contínuas-      |

|---------------------------------------------------------------------------------------------------|

| modelo/ linhas tracejadas- Experimentais)                                                         |

| Figura 5.21 – Resultados de simulação de $V_A$ para $i_f$ =0,1 - canal P (linhas contínuas-       |

| modelo/ linhas tracejadas- experimentais)                                                         |

| Figura 5.22 – Resultados de simulação de $V_A$ para $i_f=1$ - canal P (linhas contínuas- modelo/  |

| linhas tracejadas- experimentais)                                                                 |

| Figura 5.23 – Resultados de simulação de $V_A$ para $i_f$ =5 - canal P (linhas contínuas- modelo/ |

| linhas tracejadas- experimentais)                                                                 |

| Figura 5.24 – Resultados de simulação de $V_A$ para $i_f$ =20 - canal P (linhas contínuas-        |

| modelo/ linhas tracejadas- experimentais)                                                         |

| Figura 5.25 – Resultados de simulação de $V_A$ para $i_f$ =100 - canal P (linhas contínuas-       |

| modelo/ linhas tracejadas- experimentais)                                                         |

| Figura 5.26 – Resultados de simulação de $V_A$ para $T_1$ canal N (linhas contínuas- modelo/      |

| linhas tracejadas- experimentais)                                                                 |

| Figura 5.27 – Resultados de simulação de $V_A$ para $T_2$ canal N (linhas contínuas- modelo/      |

| linhas tracejadas- experimentais)                                                                 |

| Figura A.1 – Junção planar entre dreno e substrato                                                |

| Figura B.1 – Conexão elétrica para extração de <i>I<sub>S</sub></i>                               |

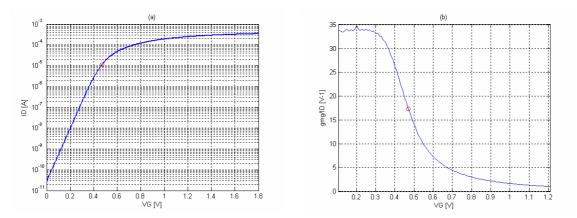

| Figura B.2 – (a) Curva $I_D x V_G$ (b) Curva $g_{mg}/I_D x V_G$                                   |

# LISTA DE ABREVIAÇÕES

ACM - Advanced Compact MOSFET Model

CLM - Channel Length Modulation (modulação do comprimento do canal)

CMOS - Complementary Metal Oxide Semiconductor

DIBL - Drain-Induced Barrier Lowering (queda da barreira de potencial

induzida pelo dreno)

MOS - Metal Oxide Semiconductor

MOSFET - Metal Oxide Semiconductor Field Effect Transistor

UCCM - Unified Charge Control Model

TSMC - Taiwan Semiconductor Manufacturing Company

## LISTA DE SIMBOLOS

ε<sub>S</sub> - permissividade elétrica do silício [C/Vm]

A<sub>i</sub> - constante de ionização por impacto [m<sup>-1</sup>]

C'<sub>OX</sub> - capacitância do óxido por unidade de área [F/m]

$F_0$  - campo elétrico no extremo da zona de depleção no lado da fonte [V/m]

F<sub>i</sub> - constante de ionização por impacto [V/m]

F<sub>L</sub> - campo elétrico no extremo da zona de depleção no lado do dreno [V/m]

g<sub>DS</sub> - condutância de saída [S]

g<sub>mg</sub> - transcondutância de porta [S]

g<sub>ms</sub> - transcondutância de fonte [S]

I<sub>D</sub> - corrente de dreno [A]

i<sub>d</sub> - corrente normalizada de dreno

I<sub>F</sub> - corrente direta [A]

i<sub>f</sub> - nível de inversão direto

i<sub>P</sub> - corrente de pinch-off normalizada

I<sub>R</sub> - corrente reversa [A]

i<sub>r</sub> - nível de inversão reverso

I<sub>s</sub> - corrente específica ou de normalização [A]

I<sub>SQ</sub> - corrente específica ou de normalização por quadrado [A]

1 - comprimento de ionização efetivo [m]

L - comprimento do canal [μm]

L<sub>ef</sub> - comprimento efetivo do canal [m]

M - fator de multiplicação de avalanche devido à ionização de impacto

n - fator de rampa

N<sub>A</sub> - concentração de aceitadores [m<sup>-3</sup>]

N<sub>D</sub> - concentração de doadores [m<sup>-3</sup>]

q - carga do elétron [C]

Q'<sub>ID</sub> - densidade de carga de inversão no terminal do dreno [C/m<sup>2</sup>]

Q'<sub>IP</sub> - densidade de carga de inversão em pinch-off [C/m<sup>2</sup>]

```

Q'<sub>IS</sub> - densidade de carga de inversão no terminal da fonte [C/m<sup>2</sup>]

```

q'<sub>ID</sub> - densidade de carga de inversão no terminal do dreno normalizada

q'<sub>IS</sub> - densidade de carga de inversão no terminal da fonte normalizada

V<sub>A</sub> - tensão de early [V]

$V_{AWA}\,$  - tensão de Early devido à Avalanche Fraca [V]

V<sub>ACLM</sub> - tensão de Early devido o CLM [V]

V<sub>ADIBL</sub> - tensão de Early devido o DIBL [V]

V<sub>B</sub> - tensão de substrato (bulk) [V]

V<sub>D</sub> - tensão de dreno (drain) [V]

$V_{DSSAT}$ - potencial  $V_{DS}$  de saturação [V]

V<sub>G</sub> - tensão de porta (gate) [V]

V<sub>P</sub> - tensão de pinch-off [V]

V<sub>S</sub> - tensão de fonte (source) [V]

V<sub>T,LC</sub> - tensão de limiar do transistor canal longo[V]

V<sub>T0</sub> - tensão de limiar [V]

W - largura do canal[μm]

y<sub>d</sub> - largura da zona de depleção do lado do dreno [m]

y<sub>s</sub> - largura da zona de depleção do lado da fonte [m]

α - parâmetro de ajuste do DIBL

$\alpha_n$  — coeficiente de ionização de impacto por unidade de área  $[m^{\text{-}1}]$

φ<sub>bi</sub> - potencial da junção [V]

φ<sub>F</sub> - potencial de Fermi [V]

φ<sub>s</sub> - potencial de superfície [V]

$\phi_{S0}$  - potencial de superfície no lado da fonte [V]

φ<sub>SL</sub> - potencial de superfície no lado do dreno [V]

$\phi_t$  - tensão termodinâmica [V]

$\mu$  - mobilidade dos portadores [m<sup>2</sup>/V.s]

σ - parâmetro DIBL

# LISTA DE TABELAS

| Tabela 5.1 – Transistores medidos.                                               | 25 |

|----------------------------------------------------------------------------------|----|

| Tabela 5.2 – Valores experimentais de <i>I<sub>S</sub></i>                       | 26 |

| Tabela 5.3 – Extração do parâmetro do DIBL                                       |    |

| Tabela 5.4 – Valores dos parâmetros obtidos pelo fitting (canal N – TSMC 0,35μm) | 42 |

| Tabela 5.5 – Valores dos parâmetros obtidos pelo fitting (canal P – TSMC 0,35μm) |    |

| Tabela 5.6 – Valores da dopagem (fabricante x ajuste)                            |    |

# 1. INTRODUÇÃO

As atuais tecnologias de integração de circuitos tornam possível que bilhões de transistores sejam construídos em uma única pastilha de circuito integrado. Para que seja possível simular ou prever resultados em circuitos de tamanha complexidade, ou até mesmo para realizar cálculos à mão em análises de primeira ordem em pequenos subcircuitos, fazse necessário o uso de um modelo eficiente [1] que represente o comportamento dos componentes do circuito.

No contexto atual da microeletrônica, o transistor MOS é um dos principais dispositivos em um circuito integrado e existem modelos baseados em física e modelos matemáticos que descrevem o comportamento do transistor em todos seus regimes de operação.

Em um projeto de eletrônica analógica e digital, diversos parâmetros do transistor MOS são necessários ao seu modelo para que o projetista possa prever resultados satisfatoriamente. Quando o transistor opera em saturação, a tensão de Early é um parâmetro fundamental, uma vez que seu valor é determinante no desempenho de circuitos como espelhos de corrente, onde influencia diretamente sua precisão, e em amplificadores de tensão, cujo ganho também depende de seu valor [2].

Neste trabalho será apresentado um modelo para a tensão de Early do transistor em saturação operando em inversão fraca e moderada levando em conta o comportamento do transistor canal curto. O foco deste modelo é o projetista de circuitos integrados, portanto são utilizadas expressões compactas, que são aproximações úteis para cálculos de primeira ordem com aplicações na eletrônica analógica e digital.

Para o cálculo da tensão de Early em saturação, as equações do modelo ACM para o transistor canal longo são aprimoradas, levando em conta os efeitos gerados pela natureza bidimensional do campo elétrico no transistor, que passam a ser mais significativos com a redução do comprimento do canal. Nesta condição, a resolução da equação de Poisson em uma dimensão se torna inválida, uma vez que o campo elétrico longitudinal possui valor significativo. Para se chegar a um modelo compacto do transistor, neste trabalho é feita uma inspeção dos efeitos gerados pelo campo elétrico longitudinal, modelando de maneira simplificada cada um destes efeitos.

Em inversão fraca e moderada, os efeitos de canal curto predominantes são o DIBL ( $Drain\ Induced\ Barrier\ Lowering$ ), o efeito da modulação do comprimento do canal através da variação do comprimento da zona de depleção na junção dreno-canal e o efeito da avalanche fraca. Tais efeitos têm por conseqüência a variação da corrente de dreno com a tensão  $V_{DS}$  aplicada para um transistor saturado, impactando na condutância de saída. Através do equacionamento dos efeitos de canal curto, é possível definir um modelo para a tensão de Early do transistor, que será determinada pela composição dos três efeitos. Em particular, daremos ênfase aos efeitos DIBL e CLM.

## 2. O TRANSISTOR CANAL LONGO

O transistor MOS (metal oxide semiconductor) é um dos principais dispositivos em um circuito eletrônico integrado, sendo extremamente necessário o uso de equações que modelem o comportamento do transistor em todos os regimes operação.

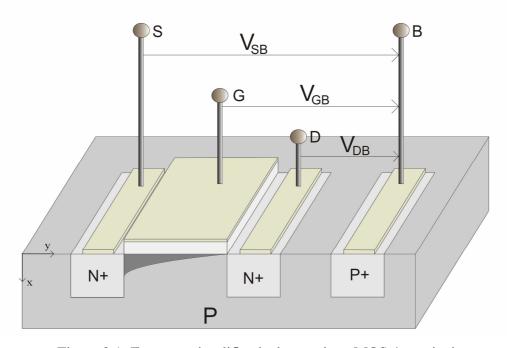

A figura 2.1 mostra um esquema ilustrativo do transistor MOS canal N de quatro terminais:

Figura 2.1- Estrutura simplificada do transistor MOS 4 terminais.

Neste dispositivo, uma tensão  $V_{GB}$  positiva aplicada fará com que os elétrons sejam atraídos até a superfície do semicondutor, formando um canal de elétrons logo abaixo do óxido de porta. Uma vez estabelecido o canal de elétrons, uma determinada diferença de potencial  $V_{DS}$  fará com que surja uma corrente  $(I_D)$  que fluirá entre o dreno e a fonte do transistor.

No modelo de canal longo utilizado, a corrente  $I_D$  pode ser modelada como a diferença entre uma corrente direta  $I_F$  (controlada pela porta e fonte) e uma corrente reversa  $I_R$  (controlada pela porta e dreno).

$$I_D = I_F - I_R = I_S (i_f - i_r) = I(V_G, V_S) - I(V_G, V_D)$$

(2.1)

sendo que:

$$I_{S} = I_{SQ} \left( \frac{W}{L} \right) \tag{2.2}$$

onde:

$$I_{SQ} = \mu C'_{ox} n \frac{\phi_t^2}{2}$$

(2.3)

$I_S$  é denominada corrente de normalização e contém parâmetros da tecnologia como a mobilidade dos portadores ( $\mu$ ), a capacitância do óxido por unidade de área ( $C'_{ox}$ ), o fator de rampa (n), parâmetros geométricos (W e L) e de temperatura ( $\phi_i$ ), já  $i_f$  e  $i_r$  são os níveis de inversão direto e reverso. Para  $i_f < 1$  considera-se que o transistor opera em inversão fraca. Para  $i_f$  entre 1 e 100, considera-se que o regime é de inversão moderada, e para  $i_f > 100$  o regime é de inversão forte.

Para o cálculo da corrente de dreno do transistor utilizam-se as componentes de difusão e deriva conforme [3]:

$$I_D = \mu W \left( -Q_I' \frac{d\phi_S}{dy} + \phi_t \frac{dQ_I'}{dy} \right)$$

(2.4)

Através da aproximação fundamental do modelo ACM [4],[5], tem-se que:

$$dQ_I' = nC_{OX}' d\phi_S \tag{2.5}$$

Substituindo (2.5) em (2.4) e integrando da fonte ao dreno tem-se:

$$I_{F(R)} = \mu C'_{OX} n \frac{W}{L} \frac{\phi_t^2}{2} \left[ \left( \frac{Q'_{IS(D)}}{n C'_{OX} \phi_t} \right)^2 - 2 \frac{Q'_{IS(D)}}{n C'_{OX} \phi_t} \right]$$

(2.6)

A equação (2.6) pode ser reescrita explicitando as densidades de carga no dreno e na fonte, em função dos níveis de inversão.

$$Q'_{IS(D)} = -nC'_{OX}\phi_t\left(\sqrt{1+i_{f(r)}} - 1\right)$$

(2.7)

Por sua vez, a relação carga tensão é dada pelo UCCM:

$$V_{P} - V_{S(D)} = \frac{-(nC'_{OX}\phi_{t} + Q'_{IS(D)})}{nC'_{OX}} + \phi_{t} \ln \left(-\frac{Q'_{IS(D)}}{nC'_{OX}\phi_{t}}\right)$$

(2.8)

Substituindo (2.7) em (2.8), chega-se a:

$$V_{P} - V_{S(D)} = \phi_{t} \left[ \sqrt{1 + i_{f(r)}} - 2 + \ln \left( \sqrt{1 + i_{f(r)}} - 1 \right) \right]$$

(2.9)

No regime de inversão fraca, a expressão (2.9) pode ser reescrita como:

$$V_P - V_{S(D)} \approx \phi_t \left[ -1 + \ln \left( \frac{i_{f(r)}}{2} \right) \right]$$

(2.10)

Para a tensão de *pinch-off*, pode-se utilizar a expressão aproximada dada por:

$$V_P \approx \frac{V_G - V_{TO}}{n} \tag{2.11}$$

Utilizando as equações (2.10) e (2.11) chega-se a uma expressão em inversão fraca para o nível de inversão em função dos potenciais nos terminais do transistor.

$$i_{f(r)} = 2.\exp\left(\frac{\frac{V_G - V_{TO}}{n} - V_{S(D)}}{\phi_t} + 1\right)$$

(2.12)

Substituindo o resultado em (2.1) e realizando algumas manipulações algébricas, obtém-se uma expressão para a corrente de dreno em função dos potenciais nos terminais do transistor.

$$I_D = 2.I_S \left\{ e^{\left(\frac{V_G - V_{TO}}{n\phi_t} + 1\right)} . e^{\left(-\frac{V_S}{\phi_t}\right)} \left[ 1 - e^{\left(\frac{-V_{DS}}{\phi_t}\right)} \right] \right\}$$

$$(2.13)$$

Esta expressão é válida para o regime de inversão fraca na região de triodo e saturação.

Considerando agora que o transistor opera em saturação, ou seja,  $i_r << i_f$ , a polarização  $V_{DS}$  deve ser maior que um potencial definido como  $V_{DSSAT}$ . A partir deste potencial, a tensão de dreno do transistor tem pouca influência sobre a corrente de dreno. Segundo [5], realizando algumas simplificações algébricas, pode-se definir um potencial  $V_{DS} = V_{DSSAT}$  a partir do qual o transistor canal longo opera em saturação.

$$V_{DSSAT} = \phi_t \left( \sqrt{1 + i_f} + 3 \right) \tag{2.14}$$

Esta expressão é uma boa aproximação para  $V_{\it DSSAT}$  em todos os regimes de inversão.

Então para  $V_{DS} > V_{DSSAT}$ , a expressão (2.13) pode ser simplificada para:

$$I_{D} = 2.I_{S}e^{\left(\frac{V_{G} - V_{TO}}{n\phi_{i}} + 1\right)}.e^{\left(-\frac{V_{S}}{\phi_{i}}\right)}$$

(2.15)

A equação (2.15) é uma boa aproximação para a corrente de dreno do transistor MOS canal longo em saturação operando em inversão fraca.

Para o regime de inversão moderada, ocorre uma transição entre as assíntotas de inversão fraca e forte, onde se dá a passagem de um regime exponencial para o regime quadrático. Neste regime, há que se considerar a expressão não explícita da corrente em função da tensão dada por (2.9).

### 3. EFEITOS DE CANAL CURTO

Com o decréscimo do comprimento do canal, o efeito do campo elétrico longitudinal se torna significativo e não mais pode ser desprezado, com ocorre no equacionamento do transistor MOS canal longo. Neste caso, a natureza bidimensional do campo elétrico deve ser levada em conta. Conforme [6], a equação de Poisson pode ser resolvida numericamente em duas dimensões [7] uma vez que a resolução analítica se torna difícil. Para o caso de dopagem uniforme, a equação de Poisson em 2-D é escrita:

$$\varepsilon_{si} \frac{\partial F_{y}}{\partial y} + \varepsilon_{si} \frac{\partial F_{x}}{\partial x} = \rho \tag{3.1}$$

Como a resolução numérica da equação de Poisson em duas dimensões é ineficiente para uso em simuladores de circuitos [8] e também não fornece solução em termos dos parâmetros tecnológicos e do dispositivo, uma maneira de modelar o comportamento do transistor canal curto é resolver a equação unidimensional de Poisson (modelo canal longo) e incluir os efeitos de canal curto através de modificações dos parâmetros do modelo canal longo. A título de exemplo, os dois principais efeitos de canal curto a serem analisados neste trabalho são o DIBL e a modulação do comprimento do canal. A forma de incluir estes efeitos é corrigir os parâmetros de canal longo, a tensão de limiar  $V_{TO}$  no caso do DIBL e o comprimento do canal no segundo caso.

Em [9] é proposto um modelo de canal curto considerando o efeito do campo elétrico longitudinal. O modelo consiste na inclusão do gradiente do campo elétrico longitudinal na resolução da equação de Poisson. É apresentada então uma expressão analítica do gradiente do campo longitudinal que possui dependência com o comprimento do canal, dada por [9],[10]:

$$E_{yy} = 2\frac{\phi_{bi} - \phi_{S0}}{L_{eff}^2} \tag{3.2}$$

onde  $E_{yy}$  é o gradiente do campo elétrico longitudinal,  $\phi_{S0}$  é o valor do potencial de superfície no lado da fonte,  $L_{eff}$  é o comprimento efetivo do canal e  $\phi_{bi}$  é o potencial da junção, dado por:

$$\phi_{bi} = \phi_t \ln \left( \frac{N_A . N_D}{n_i^2} \right) \tag{3.3}$$

A redução na tensão de limiar apresentada depende linearmente de  $E_{yy}$  para  $E_{yy} \le 10^9$   $V/cm^2$ . Para valores superiores de gradiente do campo longitudinal, a dependência de  $\Delta V_{th}$  com  $E_{yy}$  passa a ser quadrática.

No presente trabalho, a representação do comportamento do transistor MOS canal curto é feita por meio das equações do modelo canal longo expostas no capítulo anterior, modificando-as através da inclusão dos efeitos de segunda ordem que são especialmente importantes para a determinação da condutância de saída em saturação.

Deste modo, são analisados os efeitos do DIBL e a largura das zonas de depleção nas junções dreno-canal e fonte-canal que são os efeitos de canal curto predominantes em baixos e médios níveis de inversão. Também é analisado o efeito de avalanche fraca, que atua praticamente em todos os regimes de inversão do transistor e predomina em altos valores de  $V_{DS}$ .

#### **3.1 DIBL**

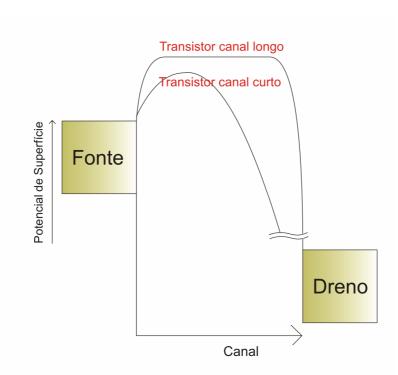

Em um transistor canal curto, o aumento da tensão de dreno causa uma queda na barreira de potencial que separa o dreno da fonte do transistor, fazendo com que ocorra um aumento da injeção de portadores por parte da fonte. Este efeito é conhecido como DIBL (queda da barreira induzida pelo dreno) e tem sido um grande limitante no escalamento de transistores MOS, pois além de aumentar a corrente de sublimiar do transistor, aumenta também a dependência da tensão de limiar com o comprimento do canal, tornando a característica tensão-corrente do dispositivo imprevisível [11]. A figura 3.1 mostra um gráfico do potencial de superfície ao longo do canal para um transistor canal longo e um canal curto conforme a referência [12].

Figura 3.1 – Variação do potencial de superfície ao longo do canal (transistor canal longo e curto).

No transistor canal longo operando em inversão fraca, o potencial de superfície é aproximadamente constante ao longo do canal. Já para um MOSFET canal curto, o potencial de superfície não é constante ao longo do canal, aparecendo um pico de potencial no lado da fonte com um valor inferior do canal longo. O valor deste pico varia com o comprimento do canal e diminui com o aumento da tensão  $V_{DS}$  aplicada.

Pode-se considerar que o DIBL resulta de dois efeitos; proximidade e penetração, conforme descrito em [13]. Em MOSFETs canal curto, a distância entre as difusões de fonte e dreno pode não ser suficiente para acomodar as regiões de depleção de ambas as difusões, até mesmo para  $V_{DS}=0$ . Neste caso, a proximidade das difusões de dreno e fonte faz com que ocorra redução da barreira de potencial em relação ao transistor canal longo. Já para  $V_{DS}>0$  ocorre o aumento da penetração do campo do dreno para a fonte. A barreira de potencial na fonte é reduzida ainda mais devido à penetração do campo, resultando em um aumento da injeção de portadores pela fonte, proporcionado um aumento na corrente de dreno.

Como exposto em [14], o efeito do DIBL aumenta conforme a penetração do campo, e depende do comprimento e perfil do canal, densidade de dopagem, profundidade da junção de fonte e dreno e da polarização de dreno e fonte.

Freqüentemente o DIBL é incluído no modelo do transistor, através de uma variação na tensão de limiar do transistor. Em [15] é apresentado um modelo para a tensão de limiar de um transistor canal curto baseado em uma solução analítica para a equação de Poisson em duas dimensões. Conforme o modelo apresentado, a tensão de limiar do transistor decresce linearmente com a polarização  $V_{DS}$  aplicada e exponencialmente com o decréscimo do comprimento do canal.

$$V_{T} = V_{T,LC} - \sigma \left[ 2(\phi_{bi} - V_{BS}) + V_{DS} \right]$$

(3.1.1)

onde  $V_{T,LC}$  é a tensão de limiar do transistor suposto de canal longo e  $\sigma$  é a magnitude do fator DIBL [15] dado por:

$$\sigma = \frac{6t_{ox}}{d_1} e^{\frac{-\pi L}{4d_1}} \tag{3.1.2}$$

onde  $d_1$  é a profundidade da zona de depleção para  $\phi_s = 2 \phi_F$  e  $t_{ox}$  é a espessura do óxido.

Uma aproximação para a tensão de limiar é proposta em [13] por meio da relação:

$$V_T = V_{T,LC} - \alpha - \beta V_{DS} \tag{3.1.3}$$

onde  $\alpha$  e  $\beta$  são parâmetros de ajuste que decrescem com o aumento do comprimento do canal. O modelo deduzido é verificado através de simulação numérica em duas dimensões.

Já em [16] o DIBL também é relacionado a uma variação linear na tensão de threshold do transistor, sendo que um modelo para a variação no potencial de superfície também é apresentado.

$$V_T = V_{T0} - (B/A)V_{DS} (3.1.4)$$

onde  $V_{T0}$  é a tensão de limiar de um transistor canal curto para  $V_{DS}=0$ , B é o parâmetro DIBL e A é o parâmetro da corrente de sublimiar (em nosso modelo A=1/n). Em transistores de canal longo, B é desprezível, e conforme o canal decresce, B cresce,

tornando a queda da barreira ainda maior. A validade destas expressões foi verificada em [12], através de simulação numérica em duas dimensões da equação de transporte de corrente. Notou-se que o valor de *B* reduz notavelmente com o aumento da dopagem do substrato, ao contrário do que prevê o modelo analítico. Para que o resultado numérico realizado fosse próximo ao modelo apresentado, ajustes nos parâmetros foram realizados.

No modelo proposto neste trabalho [17],[18], a inclusão do efeito DIBL é dada através variação linear na tensão de limiar do dispositivo causada por uma variação nas tensões de dreno e fonte, conforme as diversas referências. A tensão de limiar de um transistor canal curto pode ser definida como:

$$V_T = V_{T,LC} - \sigma [(\phi_{bi} + V_{SB}) + (\phi_{bi} + V_{DB})]$$

(3.1.5)

A equação (3.1.5) é uma forma modificada de (3.1.1) efetuada para enfatizar a simetria dreno-fonte.

Como o efeito do DIBL predomina em inversão fraca, a expressão (3.1.5) pode ser substituída na equação da corrente de dreno canal longo (2.15), chegando-se a uma expressão para a corrente de dreno em inversão fraca levando em conta o efeito do DIBL .

$$I_{D} = 2.I_{S}e^{\left(\frac{V_{G} - V_{T,LC} + \sigma[(\phi_{bi} + V_{SB}) + (\phi_{bi} + V_{DB})]}{n\phi_{t}} + 1\right)} e^{\left(-\frac{V_{S}}{\phi_{t}}\right)}$$

(3.1.6)

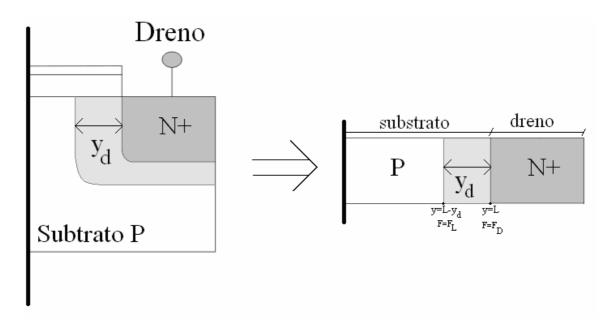

## 3.2 Zonas de depleção

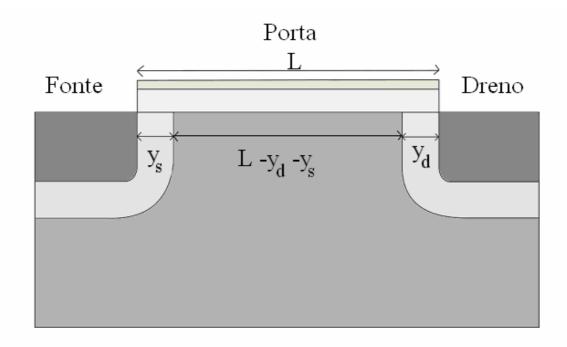

Na interface de um transistor MOS, o canal pode ser dividido em três regiões: a junção fonte-canal, de comprimento  $y_s$ , a junção dreno-canal, de comprimento  $y_d$ , e a região central do canal, com comprimento L- $y_s$ - $y_d$ ; representadas na figura 3.2 [19].

Figura 3.2 – Zonas de depleção nas junções de transistores MOS.

Em um transistor MOS de canal curto, as zonas de depleção das junções fontesubstrato e dreno-substrato podem ser significativas comparadas ao comprimento total do canal e devem ser levadas em conta no cálculo do comprimento efetivo do canal. Como o potencial de fonte geralmente é conectado ao substrato e permanece invariante nos experimentos deste trabalho, o comprimento da zona de depleção de fonte também permanecerá constante. Deste modo a variação do comprimento da zona de depleção de fonte será desconsiderada.

Uma vez que se considera que o canal sofre um encurtamento exclusivo à zona de depleção de dreno, pode-se definir um comprimento de canal efetivo.

$$L_{ef} = L - y_d \tag{3.2.1}$$

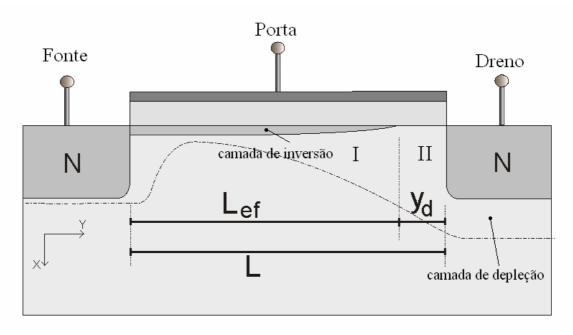

Desta maneira, o canal pode ser divido em duas regiões, uma ao longo do canal onde a aproximação canal gradual é válida (considera que o campo transversal é muito maior que o campo longitudinal), e outra próxima ao dreno, onde será realizada a análise da junção planar *one sided* formada entre dreno e substrato. Na figura 3.3 estas regiões são denominadas de I e II respectivamente.

Figura 3.3 – Distribuição de cargas em um transistor MOS em saturação.

Para o cálculo do campo longitudinal na região I, segundo [30] tem-se que:

$$I_{D} = -W\mu Q_{I}' \frac{\partial V_{C}}{\partial y}$$

(3.2.2)

Por meio do UCCM, tem-se:

$$\partial V_C = \partial Q_I' \left( \frac{1}{nC_{ox}'} - \frac{\phi_t}{Q_I'} \right) \tag{3.2.3}$$

Substituindo (3.2.3) em (3.2.2), chega-se a:

$$I_{D} = -W\mu Q_{I}' \left( \frac{1}{nC_{ox}'} - \frac{\phi_{I}}{Q_{I}'} \right) \frac{\partial Q_{I}'}{\partial y}$$

(3.2.4)

Através da aproximação fundamental do modelo ACM (2.5), a equação (3.2.4) pode ser escrita de forma normalizada como:

$$i_d = \frac{2L(q_I' + 1)}{\phi_t} \frac{\partial \phi_s}{\partial y}$$

(3.2.5)

onde

$$q'_I = Q'_I / (-nC'_{ox}\phi_I)$$

e  $i_d = \frac{I_D}{I_S}$ .

Portanto, através de (3.2.5) o campo elétrico longitudinal em um determinado ponto do canal é dado por:

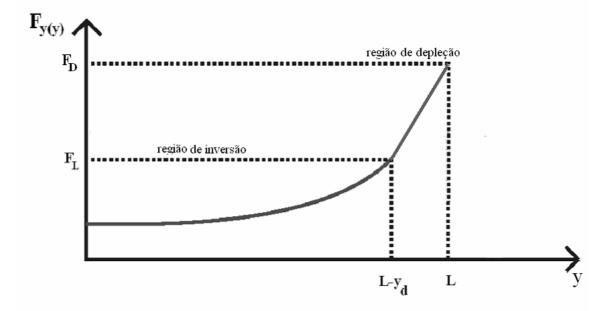

$$F_{y}(y) = -\frac{\partial \phi_{s}(y)}{\partial y} = -\frac{i_{d}\phi_{t}}{2L(q'_{t}(y)+1)}$$

(3.2.6)

Usando continuidade do campo elétrico longitudinal na passagem da camada de inversão para a zona de depleção de dreno, pode-se calcular o valor do campo em  $y=(L-y_d)_+$ .

$$F_{y}(L - y_{d})_{-} = F_{y}(L - y_{d})_{+} = F_{L} = -\frac{i_{d}\phi_{t}}{2L(q'_{ID} + 1)}$$

(3.2.7)

De acordo com [21] o perfil do campo elétrico longitudinal ao longo do canal tem o aspecto ilustrado na figura 3.4.

Figura 3.4 – Perfil do campo elétrico ao longo do canal.

De y=0 até  $y=L-y_d$  o valor do campo elétrico é dado considerando-se a aproximação de canal gradual (equação 3.2.6). A partir de  $y=L-y_d$  até y=L, que corresponde à zona de depleção de dreno, o campo longitudinal passa a ser dominante, já o campo transversal será desconsiderado. Nesta região será realizada a análise da junção N<sup>+</sup>P planar *one sided* formada entre dreno e substrato, com o dreno muito mais dopado que o substrato.

Aplicando a equação de Poisson em uma dimensão (considerando somente o campo longitudinal) na zona de depleção, obtém-se uma expressão para o comprimento da zona de depleção de dreno (ver apêndice A):

$$y_d = \sqrt{\left(\frac{F_L}{2a}\right)^2 + \frac{\phi_{bi} + V_{DB} - \phi_{SL}}{a}} - \frac{|F_L|}{2a}$$

(3.2.8)

onde:

$$a = \frac{qN_A}{2\varepsilon_S},\tag{3.2.9}$$

$\phi_{SL}$  é o potencial de superfície em  $y=L-y_d$ . Em inversão fraca,  $\phi_{SL}\approx\phi_{sa}$ . Já  $\phi_{sa}$  é dado por:

$$\phi_{sa} \approx V_P + 2\phi_F + \phi_t \tag{3.2.10}$$

sendo que:

$$V_P \approx \phi_t \left[ \sqrt{1 + i_f} - 2 + \ln(\sqrt{1 + i_f} - 1) \right] + V_{SB}$$

(3.2.11)

então:

$$\phi_{sa} \approx 2\phi_F + \phi_t \left[ \sqrt{1 + i_f} - 1 + \ln(\sqrt{1 + i_f} - 1) \right] + V_{SB}$$

(3.2.12)

Com o resultado obtido para o campo elétrico no limite entre as duas zonas, o comprimento da zona de depleção de dreno pode ser expresso por:

$$y_{d} = \sqrt{\left(\frac{i_{d}\phi_{t}}{4aL(q'_{id}+1)}\right)^{2} + \frac{\phi_{bi} + V_{DB} - \phi_{SL}}{a}} - \frac{i_{d}\phi_{t}}{4aL(q'_{id}+1)}$$

(3.2.13)

Nota-se que conforme  $V_{DB}$  aumenta, ocorre um aumento da zona de depleção da junção dreno-substrato, que modula o comprimento canal, gerando um aumento na corrente de dreno. Este efeito, além do DIBL, faz com que a corrente de dreno em saturação direta não seja constante, possuindo então uma variação com a tensão  $V_{DB}$  aplicada.

Em [22] uma expressão para a inclusão da modulação do comprimento do canal devido à saturação da velocidade dos portadores é apresentada, sendo que o foco se encontra no regime de inversão forte. De maneira semelhante pode ser introduzindo o efeito da modulação do comprimento do canal devido à zona de depleção de dreno na equação da corrente de dreno do transistor canal longo em inversão fraca (2.15):

$$I_D = 2. \frac{I_S}{1 - \left(\frac{y_d}{L}\right)} e^{\left(\frac{V_G - V_{TO}}{n\phi_t} + 1\right)} e^{\left(\frac{V_S}{\phi_t}\right)}$$

$$(3.2.14)$$

## 3.3 Avalanche fraca [23],[24],[25]

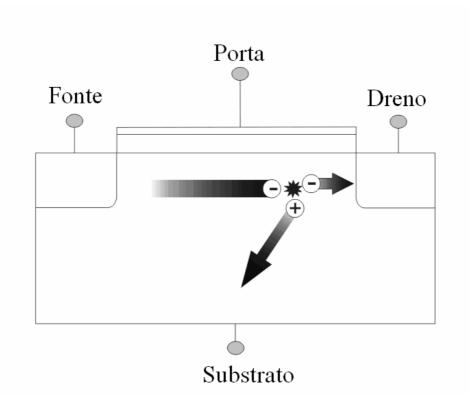

Na região do canal próxima do dreno, o campo elétrico se torna mais alto quanto maior a proximidade da junção de dreno. Se a polarização  $V_{DS}$  for alta o suficiente, elétrons atravessando a seção de campo elétrico elevado podem gerar pares elétron-lacuna por meio de ionização através de impacto. O número de pares elétron-lacuna gerados é maior quanto maior o campo elétrico, logo, haverá aumento de pares gerados conforme  $V_{DS}$  aumenta. Os elétrons gerados causam aumento na corrente de dreno, já as lacunas são supridas pelo substrato, aumentando a corrente  $I_B$  do dispositivo, conforme a figura a seguir.

Figura 3.5 – Ionização através de impacto.

Então, considerando o efeito da ionização através de impacto, e considerando que a corrente de porta é nula, tem-se:

$$I_D = I_S + I_B \tag{3.3.1}$$

A corrente de substrato gerada é uma fração da corrente de dreno [26] e pode ser representada por :

$$I_B = (M - 1)I_D (3.3.2)$$

onde M é o fator de multiplicação de avalanche devido à ionização de impacto, dado por:

$$M = \frac{1}{1 - \int \alpha_n dy} \tag{3.3.3}$$

$\alpha_n$  é o coeficiente de ionização de impacto por unidade de área e tem grande dependência do campo elétrico. A equação (3.3.4) é uma forma comum de representar a dependência de  $\alpha_n$  com o campo elétrico [27].

$$\alpha_n = A_i e^{\left(\frac{-F_i}{F}\right)} \tag{3.3.4}$$

onde  $A_i$  e  $F_i$  são chamados de constantes de ionização por impacto e F é o campo elétrico.

Como  $I_B$  é muito inferior a  $I_D$ ,  $M \approx I$  então através das equações (3.3.2) e (3.3.3) pode-se escrever:.

$$I_{B} = I_{D} \int_{y=0}^{y=1} \alpha_{n} dy$$

(3.3.5)

Sendo que y=0 representa o ponto onde ocorre o começo da ionização de impacto, e l pode ser considerado como o comprimento efetivo de ionização.

Através de (3.3.4) pode-se perceber que o efeito de avalanche fraca predomina na posição onde o campo elétrico é máximo, visto o caráter exponencial do coeficiente  $\alpha_n$  com  $F_i$ . Então se considera que o efeito de avalanche fraca predomina na região próxima ao dreno.

Substituindo (3.3.4) em (3.3.5) e calculando o campo elétrico no canal, considerando que seu valor no final do canal é muito maior que o campo em y=0, chega-se à expressão para a corrente de substrato [24] levando em conta somente o efeito de avalanche fraca:

$$I_{B} \cong I_{D} \frac{A_{i} \left(V_{DS} - V_{DSsat}\right)}{F_{i}} e^{\left(\frac{-lF_{i}}{V_{DS} - V_{DSsat}}\right)}$$

$$(3.3.6)$$

## 4. TENSÃO DE EARLY

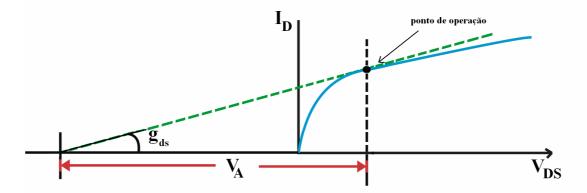

## 4.1 Definição de V<sub>A</sub>

Neste trabalho, pretende-se obter um modelo para a tensão de Early do transistor operando em saturação. Neste regime de operação a tensão de dreno tem pouca influência sobre a corrente de dreno, no caso de um transistor de canal longo. A condição para que o transistor opere saturado é que o potencial  $V_{DS}$  aplicado seja superior a um potencial definido como  $V_{DSSAT}$  (2.14). Satisfeita esta condição, a corrente de dreno do transistor de canal longo encontra-se saturada em relação à tensão de dreno. Observado as equações do transistor canal longo em inversão fraca (2.13), percebe-se que para um valor de  $V_{DS}$  suficientemente grande ( $V_{DS} > V_{DSSAT}$ ), a equação tende a seu comportamento em saturação descrito pela equação (2.15).

Para o transistor de canal curto, outros fatores devem ser levados em conta no cálculo do potencial  $V_{DSSAT}$ , mas em inversão fraca/moderada, a equação (2.14) ainda é uma boa aproximação para  $V_{DSSAT}$ . Este potencial é um valor aproximado a partir do qual os efeitos de canal curto passam a ter maior importância para determinação da variação da corrente de dreno.

A condutância de saída do transistor é definida como a variação da corrente com a variação do potencial  $V_{DS}$  aplicado em um determinado ponto de operação

$$g_{ds} = \frac{\partial I_D}{\partial V_D} \tag{4.1.1}$$

A tensão de Early é definida através da intersecção da reta tangente ao ponto de operação com o eixo de tensão de dreno. Algebricamente a tensão de Early é dada por:

$$\frac{1}{V_A} = \frac{1}{I_D} \frac{\partial I_D}{\partial V_D} = \frac{g_{ds}}{I_D} \tag{4.1.2}$$

Na figura a seguir estão indicadas a condutância de saída e a tensão de Early do transistor.

Figura 4.1 – Tensão de Early e Condutância de saída.

#### 4.2 Cálculo de VA

Após a inclusão dos efeitos de canal curto no cálculo da corrente do transistor MOS, pode-se calcular a tensão de Early associada com cada um dos efeitos modelados. Os efeitos modelados neste trabalho são considerados desacoplados, portanto admite-se que cada efeito atua de maneira exclusiva na corrente de dreno do transistor [28]. Fazendo tais considerações, pode-se dizer que:

$$\frac{\Delta I_D}{I_D} \cong \frac{1}{I_D} \left[ \frac{\partial I_D}{\partial V_D} \Big|_{DIBL} \Delta V_D + \frac{\partial I_D}{\partial V_D} \Big|_{CLM} \Delta V_D + \frac{\partial I_D}{\partial V_D} \Big|_{WA} \Delta V_D \right]$$

(4.2.1)

logo:

$$\frac{1}{V_A} = \frac{1}{V_{ADIBL}} + \frac{1}{V_{ACLM}} + \frac{1}{V_{AWA}}$$

(4.2.2)

Para o calculo da tensão de Early utilizando a corrente de fonte ao invés da corrente de dreno, a equação (4.2.2) pode ser reescrita desconsiderando-se o efeito da avalanche fraca:

$$\frac{1}{V_A} = \frac{1}{V_{ADIBL}} + \frac{1}{V_{ACLM}} \tag{4.2.3}$$

#### $4.2.1 V_{ADIBL}$

Calculando a tensão de Early associada ao efeito DIBL, tem-se que:

$$\frac{1}{V_{A_{DIRL}}} = \frac{1}{I_D} \cdot \frac{\partial I_D}{\partial V_D} \bigg|_{DIRL} \tag{4.2.1.1}$$

onde:

$$\frac{\partial I_D}{\partial V_D} = \frac{\partial I_D}{\partial q'_{is}} \frac{\partial q'_{is}}{\partial V_P} \frac{\partial V_P}{\partial V_D} \frac{\partial V_T}{\partial V_D}$$

(4.2.1.2)

A partir de agora iremos denominar  $i_d = I_D/I_S$  como a corrente  $I_D$  normalizada.

Calculando as derivadas, através de (2.6) e (2.7), tem-se:

$$\frac{\partial I_D}{\partial q'_{is}} = 2I_S \sqrt{1 + i_d} \tag{4.2.1.3}$$

Através do UCCM pode ser calculada a derivada de  $q'_{is}$  em relação a  $V_P$ .

$$\frac{\partial q'_{is}}{\partial V_P} = \frac{q'_{is}}{\phi_t(q'_{is} + 1)} = \frac{\sqrt{1 + i_d} - 1}{\phi_t \sqrt{1 + i_d}}$$

(4.2.1.4)

As expressões (4.2.1.3) e (4.2.1.4) são válidas para  $q'_{ID} << q'_{IS}$ . Utilizando a expressão para a tensão de pinch-off, tem-se que:

$$\frac{\partial V_P}{\partial V_T} = \frac{-1}{n} \tag{4.2.1.5}$$

E finalmente, considerando que a tensão de limiar do transistor possui uma dependência linear com a polarização  $V_{DB}$  (conforme equação 3.1.5), pode-se escrever que:

$$\frac{\partial V_T}{\partial V_D} = -\sigma \tag{4.2.1.6}$$

Substituindo as expressões obtidas na equação da tensão de Early devido ao DIBL e realizando algumas manipulações algébricas, tem-se :

$$V_{A_{DIBL}} = \frac{n\phi_t}{2\sigma} \left( \sqrt{1 + i_d} + 1 \right) \tag{4.2.1.8}$$

Através deste resultado pode-se observar que a parcela da tensão de Early devido ao DIBL varia muito pouco com a polarização  $V_{DS}$  aplicada, e em inversão fraca  $(i_d < I)$ , é quase independente do nível de inversão.

#### $4.2.2 V_{ACLM}$

Calculando a tensão de Early associada ao efeito modulação do comprimento do canal através da variação do comprimento da zona de depleção de dreno, tem-se que:

$$\frac{1}{V_{A_{CIM}}} = \frac{1}{I_D} \cdot \frac{\partial I_D}{\partial V_D} \bigg|_{CIM} \tag{4.2.2.1}$$

onde:

$$\frac{\partial I_D}{\partial V_D} = \frac{\partial I_D}{\partial y_d} \frac{\partial y_d}{\partial V_D}$$

(4.2.2.2)

Para o cálculo da derivada de  $I_D$  em relação a  $y_d$ , pode-se reescrever a equação (3.2.14) considerando que os termos independentes da tensão  $V_D$ , são representados por  $I_0$ , então:

$$I_{D} = \frac{I_{0}}{1 - \left(\frac{y_{d}}{L}\right)} \tag{4.2.2.3}$$

logo:

$$\frac{\partial I_D}{\partial y_d} = \frac{I_0}{L \left[1 - \left(\frac{y_d}{L}\right)\right]^2} \tag{4.2.2.4}$$

e através de (3.2.13) pode-se calcular:

$$\frac{\partial y_d}{\partial V_D} = \frac{1}{2a\sqrt{\left(\frac{F_L}{2a}\right)^2 + \frac{\phi_{bi} + V_{DB} - \phi_{SL}}{a}}}$$

(4.2.2.5)

Substituindo as expressões obtidas na equação da tensão de Early devido as zonas de depleção, tem-se:

$$V_{A_{CLM}} = 2a[L - y_d] \sqrt{\left(\frac{F_L}{2a}\right)^2 + \frac{\phi_{bi} + V_{DB} - \phi_{SL}}{a}}$$

(4.2.2.6)

Através de (3.2.1) e (3.2.6), e considerando  $V_{SB}=0$ , tem-se que:

$$V_{A_{CLM}} = 2aL_{ef} \sqrt{\frac{V_{DB}}{a} + \left\{ \left( \frac{i_d \phi_t}{4aL} \right)^2 - \frac{\phi_t \left[ \sqrt{1 + i_d} - 1 + \ln\left( \sqrt{1 + i_d} - 1 \right) \right]}{a} \right\} + \frac{\left( \phi_{bi} - 2\phi_F \right)}{a}}$$

(4.2.2.7)

#### $4.2.3 V_{AWA}$

Para o calculo da tensão de Early associada ao efeito de avalanche fraca, considerase que:

$$\frac{1}{V_{A_{WA}}} = \frac{1}{I_D} \cdot \frac{\partial I_D}{\partial V_D} \bigg|_{WA} = \frac{1}{I_D} \cdot \frac{\partial I_D}{\partial I_B} \cdot \frac{\partial I_B}{\partial V_D}$$

(4.2.3.1)

Através de (3.3.6), levando-se em conta somente o efeito de avalanche fraca para a determinação de  $I_B$ , pode-se determinar a variação de  $I_D$  com  $I_B$ .

$$\frac{\partial I_D}{\partial I_B}\bigg|_{WA} = \frac{F_i}{A_i (V_{DS} - V_{DSsat})} e^{\left(\frac{IF_i}{V_{DS} - V_{DSsat}}\right)} \tag{4.2.3.2}$$

Derivando-se a expressão para a corrente de substrato (3.3.6) em relação a  $V_D$ , temse que:

$$\frac{\partial I_{B}}{\partial V_{D}} = \frac{I_{D} \frac{A_{i}}{F_{i}} e^{\left(\frac{-lF_{i}}{V_{DS} - V_{DS_{SAT}}}\right)} \left(1 + \frac{lFi}{\left(V_{DS} - V_{DS_{SAT}}\right)}\right)}{\left(1 - \frac{A_{i}}{F_{i}} e^{\left(\frac{-lF_{i}}{V_{DS} - V_{DS_{SAT}}}\right)} \left(V_{DS} - V_{DS_{SAT}}\right)\right)} \tag{4.2.3.3}$$

Substituindo os resultados em (4.2.3.1), chega-se a uma expressão para  $V_{AWA}$ .

$$V_{A_{WA}} = \frac{\left[1 - \frac{A_{i}}{F_{i}} e^{\left(\frac{-lF_{i}}{V_{DS} - V_{DS_{SAT}}}\right)} \left(V_{DS} - V_{DS_{SAT}}\right)\right] \left(V_{DS} - V_{DS_{SAT}}\right)}{1 + \frac{lF_{i}}{\left(V_{DS} - V_{DS_{SAT}}\right)}}$$

(4.2.3.4)

No capítulo 5, o modelo da tensão de Early será comparado com os resultados experimentais, sendo que o efeito da avalanche fraca não será contabilizado, pois nas medidas será utilizada a corrente de fonte do transistor ao invés da corrente de dreno.

# 5. EXTRAÇÃO DE PARÂMETROS E RESULTADOS EXPERIMENTAIS

Neste capítulo são apresentados a metodologia e os resultados experimentais da extração dos parâmetros utilizados no modelo. Os transistores teste utilizados são das tecnologias 0,18 e 0,35µm. Na tabela a seguir consta a relação dos transistores medidos.

|                | TSMC – 0,18μm (canal N) |         | TSMC – 0,35μm (canal N e P) |                      |         |         |

|----------------|-------------------------|---------|-----------------------------|----------------------|---------|---------|

| Transistor     | Comprimento             | Comp.   | Comp.                       | Comprimento          | Comp.   | Comp.   |

|                | (L <sub>min</sub> )     | nominal | efetivo                     | (L <sub>min</sub> )  | nominal | efetivo |

|                |                         | (µm)    | (µm)                        |                      | (µm)    | (µm)    |

| $T_1$          | L=1.L <sub>min</sub>    | 0,2     | 0,18                        | L=1.L <sub>min</sub> | 0,4     | 0,35    |

| $T_2$          | L=2.L <sub>min</sub>    | 0,4     | 0,38                        | L=2.L <sub>min</sub> | 0,8     | 0,75    |

| T <sub>3</sub> | L=4.L <sub>min</sub>    | 0,8     | 0,78                        | L=4.L <sub>min</sub> | 1,6     | 1,55    |

| $T_4$          | L=8.L <sub>min</sub>    | 1,6     | 1,58                        | L=8.L <sub>min</sub> | 3,2     | 3,15    |

Tabela 5.1 – Transistores medidos.

Cada um dos transistores testados é uma associação de 10 transistores em paralelo. A razão W/L nominal é igual a 100 para cada associação de transistores. O comprimento efetivo do transistor é considerado como sendo o comprimento nominal projetado decrescido do valor médio das difusões laterais fornecido pelo fabricante para as tecnologias consideradas.

Para as medidas realizadas foram analisadas várias pastilhas de circuito integrado, procurando determinar se haveria uma variação estatística muito grande de comportamento entre chips diferentes. Como as diferenças entre chips se mostraram pouco significantes, serão expostos nesta parte experimental os resultados de extração para um único chip.

## 5.1 Extração de I<sub>S</sub>

Inicialmente deve-se determinar a corrente específica  $I_S$  dos transistores teste, pois o modelo utilizado para a descrição dos efeitos canal curto é função da corrente de polarização normalizada.

O método de extração de  $I_S$  utilizado [29] é baseado na razão entre a transcondutância de porta  $(g_{mg})$  e a corrente de dreno. A metodologia de extração de  $I_S$  está descrita no apêndice B.

Na tabela 5.2 estão os valores de  $I_S$  obtidos através da extração utilizando o método proposto para os transistores citados anteriormente.

Transistor  $0.35 \mu m (P)$  $0.18 \mu m (N)$  $0.35 \mu m (N)$  $T_1$  (L=1.L<sub>min</sub>)  $20,2\mu A$  $7,65 \mu A$  $1,63 \mu A$  $15,1 \mu A$  $6,49 \mu A$  $1,17\mu A$  $T_2$  (L=2.L<sub>min</sub>)  $T_3$  (L=4.L<sub>min</sub>) 6,69µA  $1,20\mu A$ 14,8μΑ  $T_4$  (L=8.L<sub>min</sub>) 15,6μΑ 6,88µA 1,21μΑ

Tabela 5.2 – Valores experimentais de  $I_S$ .

Como os transistores possuem mesma razão geométrica, os valores de corrente específica obtidos foram muito próximos, sendo que para o transistor de canal mínimo este valor foi um pouco maior, uma vez que a influência do  $\Delta L$  é maior neste transistor.

## 5.2 Curvas experimentais

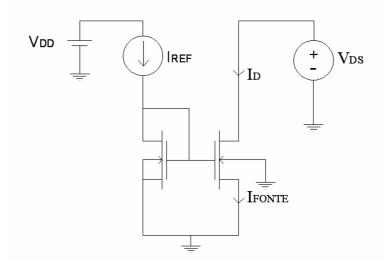

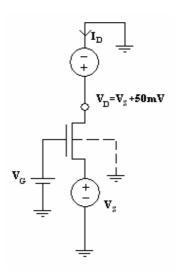

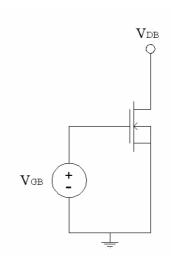

A tensão de Early e a condutância de saída são determinadas a partir do circuito da figura 5.1, para diversos níveis de inversão do transistor, impostos através da corrente  $I_{REF}$  aplicada no transistor da esquerda, sendo que os dois transistores possuem dimensões iguais.

Figura 5.1 – Conexão elétrica para extração da curva  $I_DxV_{DS}$ . (transistores canal N).

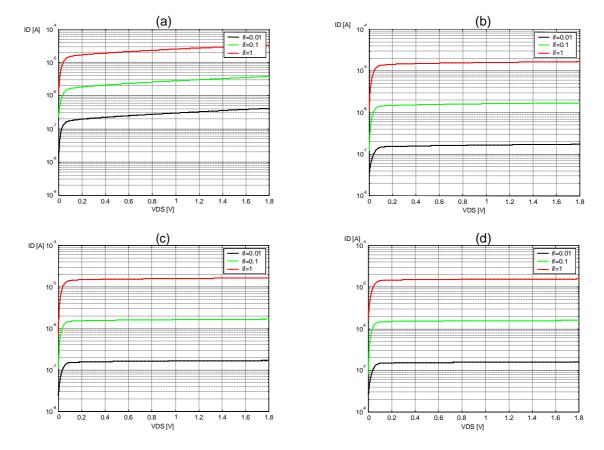

Para a extração da curva,  $I_{REF}$  é ajustado para o nível de inversão desejado, uma vez que  $I_{SI}$  é conhecido, e então  $V_D$  é excursionado de 0 a  $V_{DD}$  e a corrente  $I_D$  é medida. Para que seja possível observar o efeito da avalanche fraca, também foi medida a corrente de fonte, onde este efeito não é observado. Já a corrente de substrato pode ser determinada de forma aproximada pelas correntes de dreno e fonte, considerando-a como a diferença entre elas. Nas curvas apresentadas nas figuras 5.2 à 5.11, as linhas sólidas são referentes à corrente de dreno e as linhas tracejadas são referentes à corrente de fonte. Na maior parte dos casos, as correntes são praticamente iguais, sendo possível identificá-las separadamente somente para altos valores de  $V_{DS}$ , onde o efeito da avalanche fraca é pronunciado.

## 5.2.1 Característica de saída experimental - $I_D \times V_{DS}$

Utilizando o circuito da figura 5.1, mediu-se a característica  $I_D$  x $V_{DS}$  para os transistores da tabela 5.1. Os níveis de inversão medidos foram  $i_f$ =0,01, 0,1, 1, 5, 20 e 100 para a tecnologia 0,35 e  $i_f$ =0,01, 0,1 e 1 para a tecnologia 0,18 $\mu$ m.

Os resultados obtidos estão nos gráficos das figuras a seguir.

Figura  $5.2 - I_D \times V_{DS}$  (TSMC  $0.18 \mu m$ ) - (a) transistor  $T_1$  (L=Lmin) - (b) transistor  $T_2$  (L=2Lmin) - (c) transistor  $T_3$  (L=4Lmin) - (d) transistor  $T_4$  (L=8Lmin).

Figura  $5.3 - I_D \times V_{DS}$  (TSMC  $0.35 \mu m$  canal N) - (a) transistor  $T_1$  (L=Lmin) - (b) transistor  $T_2$  (L=2Lmin) - (c) transistor  $T_3$  (L=4Lmin) - (d) transistor  $T_4$  (L=8Lmin).

Para melhor observar o efeito da avalanche fraca, a figura a seguir mostra um detalhe na corrente do transistor  $T_2$  da tecnologia  $0.35\,\mu\text{m}$ , com  $i_f$ =0.01. A linha tracejada representa a corrente de fonte do transistor e a linha contínua a corrente de dreno. Nota-se que para valores mais altos de  $V_{DS}$ , ocorre a divergência entre a corrente de dreno e fonte, evidenciando o efeito de avalanche fraca.

Figura 5.4 – Detalhe da corrente do transistor  $T_2$ .

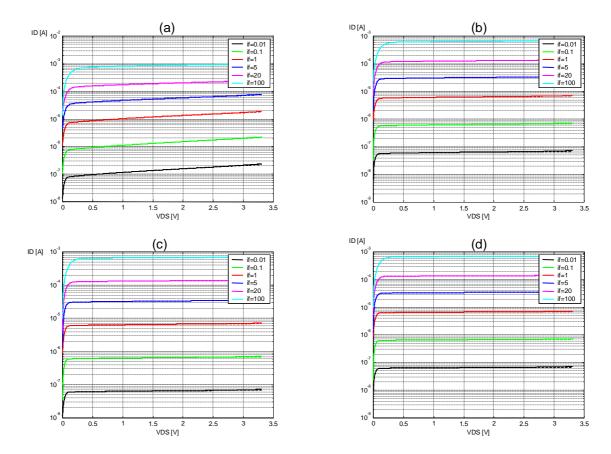

## 5.2.2 Condutância de saída experimental - $g_{ds} \times V_{DS}$

Utilizando a curva  $I_D$  x  $V_{DS}$  pode ser calculado o valor da condutância de saída dos transistores para cada ponto de operação fazendo-se a derivada da corrente  $I_D$  em relação a  $V_{DS}$ , conforme equação (4.1.1). O cálculo da curva foi feito através do programa Matlab, utilizando a função de alisamento SPAPS para redução do ruído da derivada.

Figura  $5.5 - g_{ds} \times V_{DS}$  (TSMC  $0.18 \mu m$ ) - (a) transistor  $T_1$  - (b) transistor  $T_2$  - (c) transistor  $T_3$  - (d) transistor  $T_4$ .

Figura 5.6 –  $g_{ds} \times V_{DS}$  (TSMC 0,35 $\mu$ m canal N) - (a) transistor  $T_1$  - (b) transistor  $T_2$  - (c) transistor  $T_3$  - (d) transistor  $T_4$ .

Através das curvas, pode-se observar que a condutância de saída aumenta com o nível de inversão, sendo que em inversão fraca, as curvas apresentam um comportamento muito semelhante para os diversos níveis de inversão, exceto por um deslocamento dado pelo valor do módulo da corrente. O valor da condutância na região triodo é muito semelhante para os diversos comprimentos de canal. Já na saturação, a condutância é maior quanto menor o comprimento do canal. Observa-se também que para comprimentos de canal mais curtos, a condutância em saturação é aproximadamente constante, o que não é observado para comprimentos maiores do canal.

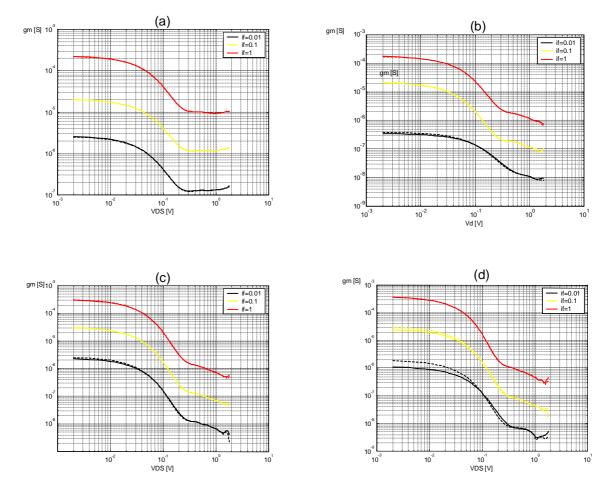

## 5.2.3 Tensão de Early experimental - $V_A \times V_{DS}$

Através da curva  $I_D \times V_{DS}$  e da definição de  $V_A$  (4.1.2), a curva experimental de  $V_A$  pode ser traçada. A determinação das curvas foi feito em Matlab utilizando o mesmo procedimento descrito no item anterior. Para observar a variação de  $V_A$  com o nível de inversão bem como com o comprimento do canal, as curvas de  $V_A$  foram traçadas para um nível de inversão fixo mostrando diversos comprimentos de canal e também foram traçadas para um comprimento fixo mostrando diversos níveis de inversão.

Os resultados experimentais de  $V_A$  obtidos estão nos gráficos das figuras a seguir.

Figura 5.7 –  $V_A$  x  $V_{DS}$  (TSMC 0,18 $\mu$ m) - Comprimento fixo para vários  $i_f$ 's - (a) transistor  $T_1$  - (b) transistor  $T_2$  - (c) transistor  $T_3$  - (d) transistor  $T_4$ .

Figura  $5.8 - V_A \times V_{DS}$  (TSMC  $0.18 \mu m$ ) -  $i_f$  fixo para vários comprimentos de canal - (a)  $i_f$ =0.01 - (b)  $i_f$ =0.1 - (c)  $i_f$ =1.

Figura  $5.9 - V_A \times V_{DS}$  (TSMC  $0.35 \mu m$  canal N) - Comprimento fixo para vários  $i_f$ 's - (a) transistor  $T_1$  - (b) transistor  $T_2$  - (c) transistor  $T_3$  - (d) transistor  $T_4$ .

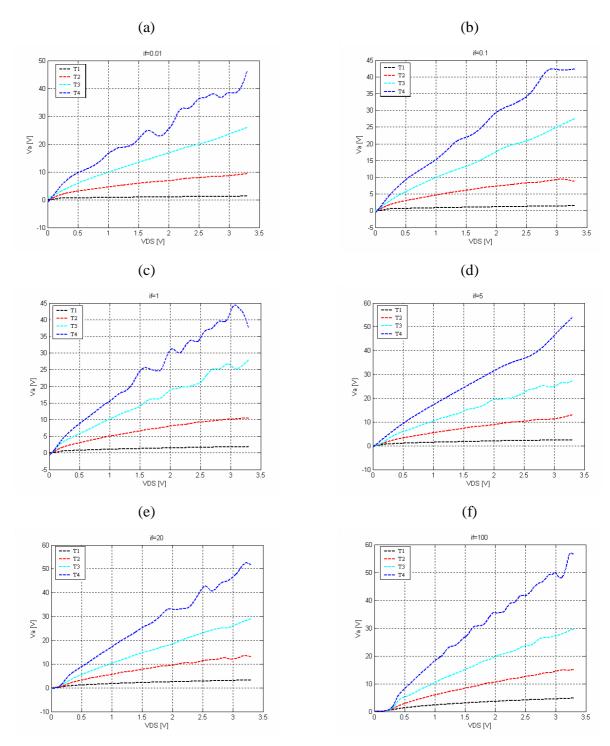

Figura  $5.10 - V_A \times V_{DS}$  (TSMC  $0.35 \mu m$  canal N) -  $i_f$  fixo para vários comprimentos de canal - (a)  $i_f$ =0.01 - (b)  $i_f$ =0.1 - (c)  $i_f$ =1 (d)  $i_f$ =5 - (e)  $i_f$ =20 - (f)  $i_f$ =100.

Figura  $5.11 - V_A \times V_{DS}$  (TSMC  $0.35 \mu m$  canal P) -  $i_f$  fixo para vários comprimentos de canal - (a)  $i_f$ =0,01 - (b)  $i_f$ =0,1 - (c)  $i_f$ =1 (d)  $i_f$ =5 - (e)  $i_f$ =20 - (f)  $i_f$ =100.

Pode-se observar através das curvas obtidas de tensão de Early em inversão fraca, que a tensão de Early é praticamente invariante com o nível de inversão, sendo que a dependência com  $i_f$  fica mais evidente a partir da inversão moderada. Esta diferença entre níveis de inversão é mais pronunciada quanto menor o tamanho de transistor. A título de exemplo (figura 5.9), a curva de tensão de Early do transistor de canal mínimo ( $T_1$ ) para  $i_f$ =0,01 é aproximadamente três vezes inferior em magnitude que a curva para  $i_f$ =100. Já para o transistor  $T_4$ , esta diferença é aproximadamente duas vezes.

## 5.3 Extração do parâmetro do DIBL

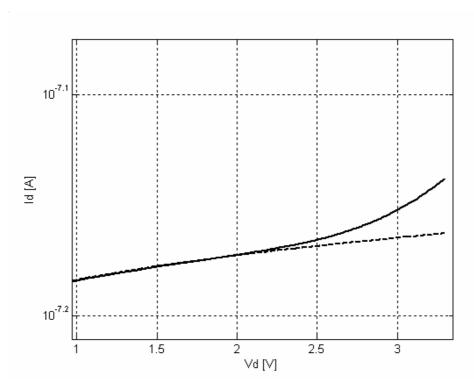

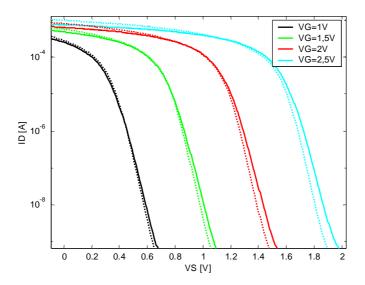

A extração do parâmetro relacionado ao DIBL será feita através da relação entre transcondutância de fonte e corrente de dreno, utilizando circuito apresentado na figura 5.12.

Figura 5.12 – Extração do parâmetro do DIBL.

No circuito da figura 5.12, a tensão de porta será ajustada para um valor fixo e então a tensão de fonte será excursionada, mantendo-se sempre  $V_{DS}$  constante e igual a 50mV para minimizar o efeito do CLM e da avalanche fraca e a corrente  $I_D$  será medida. Este procedimento é realizado para  $V_G$ =0,35, 0,5, 1,0, 1,5, 2,0, 2,5 e 3,0. Na figura 5.13, as curvas tracejadas foram obtidas para um transistor de canal aproximadamente longo (T<sub>4</sub>) e as contínuas para um transistor de canal curto (T<sub>1</sub>) com  $V_G$ =1, 1,5 2,0 e 2,5 V.

Figura  $5.13 - I_D \times V_S$  para um transistor de canal longo (tracejado) e um de canal curto (contínuo).

Calculando a derivada logarítmica da corrente em relação a  $V_S$  obtém-se o valor da razão transcondutância de fonte por corrente de dreno:

$$\frac{g_{ms}}{I_D} = \frac{\partial \ln(I_D)}{\partial V_S} \tag{5.3.1}$$

Como se pode observar, em inversão fraca a inclinação das curvas expostas na figura 5.13 é constante para uma variação logarítmica de  $I_D$ , uma vez que a relação entre corrente e tensão é exponencial neste regime de inversão. Neste regime, a razão  $g_{ms}/I_D$  será aproximadamente constante e possuirá seu valor máximo em módulo.

De acordo com [12], pode-se determinar analiticamente o valor da transcondutância de fonte por corrente de dreno para o transistor canal longo em inversão fraca no circuito da figura 5.12.

$$\frac{g_{ms}}{I_D} = -\frac{1}{\phi_t} \tag{5.3.2}$$

Para um transistor de canal curto em inversão fraca, sob o efeito do DIBL, considerando  $V_{DS}$  constante, o valor da transcondutância é inferior, sendo dado por:

$$\frac{g_{ms}}{I_D} = \frac{1}{\phi_t} \left( 1 - \frac{2\sigma}{n} \right) \tag{5.3.3}$$

No apêndice C encontra-se a dedução da equação (5.3.3). Como pode-se observar, em inversão fraca, a razão  $g_{ms}/I_D$  de um transistor é aproximadamente constante com  $V_S$ , portanto será na inversão fraca a extração de  $2\sigma/n$ . Então, obtendo-se o valor da transcondutância de fonte de um transistor de canal longo pode-se calcular o valor de  $2\sigma/n$  para um transistor de canal curto através de sua transcondutância.

$$\frac{g_{ms_{c.curto}}}{I_D} = \frac{g_{ms_{c.longo}}}{I_D} \left(1 - \frac{2\sigma}{n}\right) \tag{5.3.4}$$

Então utilizando os valores experimentais da inclinação das curvas  $ln(I_D)$  x  $V_S$ , as equações (5.3.1) e (5.3.4), pode-se calcular a razão  $2\sigma/n$  para os transistores de canal curto tendo como referência de canal longo, o transistor  $T_4$ . Os valores obtidos para os transistores  $T_1$  e  $T_2$  com  $V_G$ =0,35V encontram-se na tabela 5.3.

Tabela 5.3 – Extração do parâmetro do DIBL

| Tecnologia | Transistor | 2σ/n  |

|------------|------------|-------|

| TSMC 0,35  | $T_1$      | 0,036 |

| TSMC 0,35  | $T_2$      | 0,026 |

Para níveis superiores de tensão de porta, o valor da razão  $2\sigma/n$  aumenta, sendo que este aumento é mais pronunciado quanto menor o comprimento do canal. Experimentalmente, foi observado que este aumento se reflete no decréscimo da tensão de Early. Para comprovação, foi utilizado o circuito da figura 5.1 com o potencial de fonte fixo em 1V ( $V_G$  se torna superior para um dado nível de inversão) e observou-se que para um mesmo  $V_{DS}$ , ocorreu um decréscimo no valor da tensão de Early, e este decréscimo foi mais significativo para o transistor de canal mais curto.

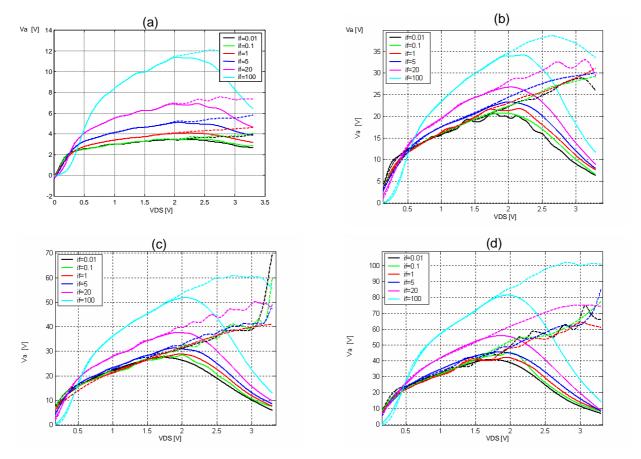

## 5.4 Simulação e ajuste de parâmetros

Através das expressões (4.2.3), (4.2.1.8) e (4.2.2.7) são traçadas as curvas teóricas da tensão de Early. Os parâmetros necessários ao modelo serão ajustados empiricamente para uma concordância mais precisa às curvas experimentais. O método utilizado para ajuste das curvas foi através de múltiplas iterações com *fitting* visual.

Os parâmetros a,  $\phi_{bi}$  e  $\phi_F$  são dependentes da tecnologia e possuem valores teóricos que podem ser usados como valores iniciais, sendo que devem ser ajustados para que as curvas simuladas e experimentais apresentem concordância satisfatória.

Nesta simulação, as curvas teóricas serão comparadas com a curva de tensão de Early obtida através da corrente de fonte, de maneira a diminuir o efeito da avalanche fraca, que não será utilizada na simulação da curva teórica.

Para a tecnologia  $0.35 \mu m$ , o valor de L utilizado é o comprimento efetivo dado na tabela 5.1. O valor de  $i_d$  é considerado como sendo o valor de  $i_f$  imposto pelo espelho de corrente da figura 5.1, de maneira a simplificar a simulação.

Inicialmente é utilizado para "a" o valor obtido através do  $N_A$  fornecido para a tecnologia TSMC 0,35. Para transistores canal N,  $N_A$ =2,2.10<sup>23</sup> m<sup>-3</sup> que leva a um valor de a=1,7.10<sup>14</sup> V/m². Para o canal P,  $N_A$ =8,5.10<sup>22</sup> m<sup>-3</sup>, portanto a= 6,5.10<sup>13</sup> V/m². Os valores correspondentes de  $N_A$ , calculados através do ajuste do parâmetro "a" e os valores fornecidos pela foundry encontram-se na tabela 5.6.

Com  $\sigma$  é um parâmetro dependente do comprimento do canal, ele é ajustado separadamente para cada comprimento de canal, já os parâmetros a,  $\phi_{bi}$  e  $\phi_F$  são universais para uma dada dopagem. Os valores de  $2\sigma/n$  extraídos e expostos na tabela 5.3 são utilizados como um valor inicial, mas se mostraram relativamente diferentes dos valores obtidos através do *fitting*. Embora haja na literatura modelos da dependência de  $\sigma$  com o comprimento do canal, como mostrado no capítulo 3, os resultados experimentais para  $\sigma$  não foram consistentes com as formulas da literatura técnica.

Para as simulações realizadas, os valores dos parâmetros obtidos que proporcionaram o melhor ajuste se encontram nas tabelas 5.4 e 5.5.

Tabela 5.4 – Valores dos parâmetros obtidos pelo fitting (canal N – TSMC 0,35μm)

|                | 2σ/n    | a [V/m <sup>2</sup> ] | $(\phi_{bi} - 2\phi_F)$ [V] |

|----------------|---------|-----------------------|-----------------------------|

| $T_1$          | 0,0117  | $2,5.10^{14}$         | 0,1                         |

| $T_2$          | 0,0013  | 2,5.10 <sup>14</sup>  | 0,1                         |

| T <sub>3</sub> | 0,001   | $2,5.10^{14}$         | 0,1                         |

| $T_4$          | 0,00075 | $2,5.10^{14}$         | 0,1                         |

Tabela 5.5 – Valores dos parâmetros obtidos pelo fitting (canal P – TSMC 0,35μm)

|                | 2σ/n    | a [V/m <sup>2</sup> ] | $(\phi_{bi} - 2\phi_F)$ [V] |

|----------------|---------|-----------------------|-----------------------------|

| $T_1$          | 0,03    | 4,3.10 <sup>13</sup>  | 0,1                         |

| $T_2$          | 0,0028  | 4,3.10 <sup>13</sup>  | 0,1                         |

| T <sub>3</sub> | 0,001   | 4,3.10 <sup>13</sup>  | 0,1                         |

| $T_4$          | 0,00075 | 4,3.10 <sup>13</sup>  | 0,1                         |

Tabela 5.6 – Valores da dopagem (fabricante x ajuste)

|         | N <sub>A</sub> Teórico (foundry)[m <sup>-3</sup> ] | N <sub>A</sub> obtido por ajuste[m <sup>-3</sup> ] |

|---------|----------------------------------------------------|----------------------------------------------------|

| Canal P | $2,2.10^{23}$                                      | 3,2.10 <sup>23</sup>                               |

| Canal N | 8,5.10 <sup>22</sup>                               | 5,62.10 <sup>22</sup>                              |

As figuras 5.14 a 5.27 apresentam as curvas de tensão de Early obtidas para diversos comprimentos de canal para a tecnologia TSMC 0,35µm, sendo que o nível de inversão é mantido fixo. As curvas tracejadas são obtidas experimentalmente e as curvas contínuas são o resultado da simulação utilizando os parâmetros já ajustados. Para minimizar o efeito da avalanche fraca, será utilizada a corrente de fonte para comparação.

Figura 5.14 – Resultados de simulação de  $V_A$  para  $i_f$ =0,01 - canal N (linhas contínuas- modelo/ linhas tracejadas- experimentais)

Figura 5.15 – Resultados de simulação de  $V_A$  para  $i_f$ =0,1 - canal N (linhas contínuas- modelo/ linhas tracejadas- experimentais)

Figura 5.16 – Resultados de simulação de  $V_A$  para  $i_f$ =1 - canal N (linhas contínuas-modelo/ linhas tracejadas- experimentais)

Figura 5.17 – Resultados de simulação de  $V_A$  para  $i_f$ =5 - canal N (linhas contínuas-modelo/ linhas tracejadas- experimentais)

Figura 5.18 – Resultados de simulação de  $V_A$  para  $i_f$ =20 - canal N (linhas contínuas-modelo/ linhas tracejadas- experimentais)

Figura 5.19 – Resultados de simulação de  $V_A$  para  $i_f$ =100 - canal N (linhas contínuas- modelo/ linhas tracejadas- experimentais)

Figura 5.20 – Resultados de simulação de  $V_A$  para  $i_f$ =0,01 - canal P (linhas contínuas- modelo/ linhas tracejadas- Experimentais)

Figura 5.21 – Resultados de simulação de  $V_A$  para  $i_f$ =0,1 - canal P (linhas contínuas-modelo/ linhas tracejadas- experimentais)

Figura 5.22 – Resultados de simulação de  $V_A$  para  $i_f$ =1 - canal P (linhas contínuas-modelo/ linhas tracejadas- experimentais)

Figura 5.23 – Resultados de simulação de  $V_A$  para  $i_f$ =5 - canal P (linhas contínuas-modelo/ linhas tracejadas- experimentais)

Figura 5.24 – Resultados de simulação de  $V_A$  para  $i_f$ =20 - canal P (linhas contínuas-modelo/ linhas tracejadas- experimentais)

Figura 5.25 – Resultados de simulação de  $V_A$  para  $i_f$ =100 - canal P (linhas contínuas- modelo/ linhas tracejadas- experimentais)

Para melhor visualizar a variação da tensão de Early com o nível de inversão nos transistores de menor comprimento, as figuras 5.26 e 5.27 mostram a tensão de Early dos transistores  $T_1$  e  $T_2$  da tecnologia TSMC  $0.35\mu m$  canal N para diversos níveis de inversão.

Figura 5.26 – Resultados de simulação de  $V_A$  para  $T_1$  canal N (linhas contínuas-modelo/ linhas tracejadas- experimentais)

Figura 5.27 – Resultados de simulação de  $V_A$  para  $T_2$  canal N (linhas contínuas-modelo/ linhas tracejadas- experimentais)

Como pode se observar através do equacionamento obtido e através da comparação com os resultados experimentais, a tensão de Early do transistor possui valor praticamente independente do nível de inversão em todo regime de inversão fraca, sendo que neste regime a dependência com  $V_{DS}$  é menor que no regime de inversão moderada, evidenciando a preponderância do DIBL para baixos níveis de inversão.

Conforme ocorre aumento do nível de inversão, ( $i_f \approx 5$ ) a tensão de Early passa a ter uma dependência maior com o nível de inversão, conforme o esperado pelo equacionamento do DIBL. A partir destes níveis de inversão, nota-se também um ligeiro aumento da dependência da tensão de Early com a polarização  $V_{DS}$ , evidenciando que a componente devido o CLM passa a ter maior influência com o aumento do nível de inversão.

O aumento do valor de  $V_A$  com aumento do comprimento do canal também pode ser observado, sendo que para comprimentos muito próximos a  $L_{min}$ , qualquer variação estatística do comprimento do canal resulta em grandes variações na tensão de Early do dispositivo, tornando difícil a avaliação experimental da dependência da tensão de Early com o comprimento do canal em transistores muito curtos.

## 6. CONCLUSÃO

Modelos mais simples que consideram a tensão de Early constante, ou proporcional a L são inadequados para representar a tensão de Early e introduzem erros que podem ser significativos no projeto de circuitos eletrônicos.

Para a análise da tensão de Early em transistores de canal curto, a natureza bidimensional do campo elétrico deve ser levada em conta na modelagem do dispositivo, uma vez que em uma grande parte do canal, o campo elétrico longitudinal não pode ser desprezado.

A resolução tanto numérica quanto analítica da equação de Poisson em duas dimensões é em geral complicada para cálculos à mão. Por outro lado, fazendo-se análise do transistor de canal longo com a inclusão dos efeitos canal curto resultantes do campo longitudinal, chega-se a equações simples e úteis ao projetista de circuitos, que precisa de um modelo eficiente para cálculos à mão em análises de primeira ordem.

Para se obter um modelo eficiente da tensão de Early operando em inversão fraca e moderada, o encurtamento do canal devido à largura das zonas de depleção e a redução da barreira de potencial induzida pelo dreno (DIBL) devem ser modelados, uma vez que são os efeitos de canal curto dominantes nestes regimes de inversão.

Foi experimentalmente verificado que para níveis de inversão  $i_f < 1$ , a tensão de Early é pouco dependente do nível de inversão, conforme antecipado pela formulação analítica aqui desenvolvida.

As aproximações de  $V_A$  obtidas através da análise são consistentes com os resultados experimentais e possuem parâmetros com significado físico, mas que para adequada representação dos resultados experimentais, tiveram de ser ajustados, para levar a resultados próximos ao esperado.

### 6.1 Trabalhos futuros

Para uma melhor comparação com os resultados experimentais, os transistores testes devem ser constituídos de associações em série de vários transistores de canal mínimo. Caso fosse utilizada esta associação, as variações  $\Delta L$  do comprimento do transistor seriam proporcionais ao numero de transistores, e passariam a ter a mesma influência em

transistores curtos e longos. Em tecnologias que possuem dopagem não uniforme como é o caso das que utilizam *pocket implants* (técnica de dopagem não uniforme que tem por objetivo reduzir efeitos de canal curto), a associação série faz com que a dopagem média do substrato seja próxima tanto para transistores de canal longo quanto para transistores de canal curto. No caso de não se utilizar a associação série, em transistores de canal curto o efeito dos *pockets implants* na dopagem média do substrato é maior do que em transistores de canal longo. Desta maneira a dopagem media do substrato será maior em transistores de menor comprimento de canal. Fazendo-se então a análise experimental da tensão de Early com associações série de transistores (a associação série é bastante utilizada em projetos de circuitos integrados) facilitará a verificação das regras geométricas.

A modelagem da tensão de Early pode ser expandida para níveis superiores de inversão, incluindo o efeito da saturação da velocidade dos portadores e levando em conta a carga de inversão.

É importante desenvolver métodos de extração para determinação mais precisa dos parâmetros associados ao DIBL e CLM, preferencialmente em regiões onde os dois efeitos possam ser separados, como é o casa da região triodo, que não é muito afetada pelo CLM.

## **APÊNDICES**

## Apêndice A - Cálculo do comprimento da zona de depleção de dreno

Para o cálculo do comprimento da zona de depleção de dreno, é utilizada a análise da junção planar formada entre dreno e substrato (figura A.1). Considera-se que esta junção é do tipo *one sided*, ou seja, ela se estende totalmente sobre o lado menos dopado, no caso o substrato. Esta consideração é válida desde que um dos lados da junção seja muito mais dopado que o outro.

Figura A.1 – Junção planar entre dreno e substrato

Aplicando a equação de Poisson para o campo na zona de depleção, tem-se:

$$\frac{\partial F}{\partial y} = \frac{\rho}{\varepsilon_{si}} \tag{A.1}$$

Considerando que a densidade volumétrica de carga  $\rho$  é  $qN_A$ , então:

$$\frac{\partial F}{\partial y} = -\frac{qN_A}{\varepsilon_{yi}} \tag{A.2}$$