#### Luiz Alberto Pasini Melek

# ANALYSIS AND DESIGN OF A SUBTHRESHOLD CMOS SCHMITT TRIGGER CIRCUIT

Tese submetida ao Programa de Pósgraduação em Engenharia Elétrica da Universidade Federal de Santa Catarina para a obtenção do Grau de Doutor em Engenharia Elétrica.

Orientador: Prof. Dr. Carlos Galup-

Montoro

Coorientador: Prof. Dr. Márcio

Cherem Schneider

Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Melek, Luiz Alberto Pasini

ANALYSIS AND DESIGN OF A SUBTHRESHOLD CMOS

SCHMITT TRIGGER CIRCUIT / Luiz Alberto Pasini Melek

; orientador, Carlos Galup-Montoro, coorientador,

Márcio Cherem Schneider, 2017.

151 p.

Tese (doutorado) - Universidade Federal de Santa Catarina, , Programa de Pós-Graduação em Engenharia Elétrica, Florianópolis, 2017.

Inclui referências.

1. Engenharia Elétrica. 2. Schmitt trigger. 3. Ultra-baixa tensão. 4. Inversão fraca. 5. Inversor CMOS. I. Galup-Montoro, Carlos. II. Schneider, Márcio Cherem. III. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia Elétrica. IV. Título.

#### Luiz Alberto Pasini Melek

## ANALYSIS AND DESIGN OF A SUBTHRESHOLD CMOS SCHMITT TRIGGER CIRCUIT

Esta Tese foi julgada adequada para obtenção do Título de "Doutor em Engenharia Elétrica", e aprovada em sua forma final pelo Programa de Pós-graduação em Engenharia Elétrica.

Florianópolis, 14 de Julho de 2017.

Prof. Marcelo Lobo Heldwein, Dr.

Coordenador do Curso

#### Banca Examinadora:

Prof. Carlos Galup-Montoro, Dr.

Orientador

Universidade Federal de Santa Catarina

Prof. Márcio Cherem Schneider, Dr. Coorientador Universidade Federal de Santa Catarina

Prof. Antônio Carlos Moreirão de Queiroz, Dr. Universidade Federal do Rio de Janeiro

## Prof. Volnei Pedroni, Dr. Universidade Tecnológica Federal do Paraná

Prof. Oscar Gouveia Filho, Dr. Universidade Federal do Paraná

William Prodanov, Dr. Chipus Microelectronics

Prof. José Luís Güntzel, Dr. Universidade Federal de Santa Catarina

#### **AGRADECIMENTOS**

Meus sinceros agradecimentos aos meus familiares, orientadores, professores, colegas de laboratório, funcionários da UFSC, membros das bancas de qualificação e de defesa desta tese, e demais amigos, sem os quais este trabalho não teria sido possível:

Ambrosio Melek, Prof. Dr. André Inácio Reis (UFRGS), Prof. Dr. André Augusto Mariano (UFPR), Andres Fernando Ordoñez Hurtado, Anselmo Luís da Silva Júnior, Arturo Fajardo Jaimes, Dr. Arun Kumar Sinha, Bruno Zimpel, Carlyle Câmara Santos Júnior, Prof. Dr. Carlos Galup-Montoro (Orientador - UFSC), Prof. Dr. Carlos Renato Rambo (UFSC), Caroline Maria Ciscato Melek, Cristina Missel Adornes, Daniel Lucas Novack, Profa. Dra. Daniela Ota Hisayasu Suzuki (UFSC), Deni Germano Alves Neto, Prof. Dr. Djones Vinícius Lettnin (UFSC), Prof. Dr. Eduardo Augusto Bezerra (UFSC), Eduardo Brandão, Profa. Dra. Elizabeth Wegner Karas (UFPR), Fabrício Silva, Prof. Dr. Fernando Rangel de Souza (UFSC), Franciele Nornberg, Fred Rockenberger, Giulia Ciprandi, Gustavo Martins, Prof. Dr. Hector Pettenghi Roldan (UFSC), Henrique Mamoru Haysaka, Dr. Illya Kokshenev (UFMG), Isabella Garcia, Prof. Dr. Jader Alves de Lima Filho (UFSC), Prof. Dr. Jefferson Luiz Brum Marques (UFSC), Jefferson Cardoso Ribeiro, João Vítor Ferreira, José Carlos Lobato Pasini, Prof. Dr. José Luís Almada Güntzel (UFSC), Juan Moya Baguero, Kaléo Turnes Silvestri, Luiz Antonio Pasini Melek, Luiz Gustavo Pasini Melek, Maicon Deivid Pereira, Marcelo Siqueira, Dr. Márcio Bender Machado (IF-SUL), Prof. Dr. Márcio Cherem Schneider (Orientador - UFSC), Mário Baldini Neto, Prof. Dr. Márlio José do Couto Bonfim (UFPR), Maria Fernanda Pasini Melek, Mariana Siniscalchi, Mateus Bernardino Moreira, Prof. Dr. Mohamad Sawan (Polytechnic School of Montreal), Nathália Della Giustina Ballmann, Nazide Martins (UFSC), Dr. Osmar Franca Siebel, Paulo Márcio Moreira e Silva, Prof. Dr. Petr Iakovlevitch Ekel (PUC-MG), Renato Silveira Feitoza, Roddy Alexander Romero Antayhua, Rodrigo Luiz de Oliveira Pinto, Ronaldo Ponte, Prof. Dr. Rui Seara (UFSC), Dr. Sheldon Lee Cooper (The Big Bang Theory), Prof. Dr. Sidnei Noceti Filho (UFSC), Dra. Siobhan Weise, Prof. Dr. Volnei Pedroni (UTFPR), Wilson Silva Costa, Vanderlei Cardoso, Yuri Juppa, Zomagboguelou Wilfried Agossou.

Também agradeço às entidades Capes e Cnpq, por financiarem parcialmente este trabalho, através da bolsa de estudos e taxa de bancada, que auxiliaram a me manter em Florianópolis durante um bom tempo.

Agradeço à Mosis pelos serviços de fabricação dos circuitos integrados gratuitos, sem os quais essa pesquisa não poderia ter sido realizada satisfatoriamente.

Agradeço ao Departamento de Engenharia Elétrica da Universidade Federal do Paraná pela autorização para realização de algumas medidas nos circuitos integrados fabricados, no período em que voltei para Curitiba.

Agradeço à Universidade Federal de Santa Catarina e ao Departamento de Engenharia Elétrica e Eletrônica por novamente me aceitarem como aluno, agora para o doutorado.

Em especial, gostaria de mais uma vez agradecer aos meus orientadores, prof. Carlos Galup-Montoro e prof. Márcio Cherem Schneider, por me aceitarem novamente no Laboratório de Circuitos Integrados, depois de um intervalo de 10 anos desde o mestrado. Agradeço pela orientação de todo o trabalho de pesquisa durante pouco mais de 4 anos, pela paciência e dedicação na revisão dos artigos publicados e desta tese e pela saudável insistência e confiança em termos bons trabalhos publicados. Agradeço por me passarem o conhecimento que adquiriram ao longo dos anos e me mostrarem o que é Pesquisa, na intenção de desenvolver a Ciência e a Tecnologia no Brasil e no Mundo, desde o primeiro dia do doutorado, quando o prof. Carlos me falou que o doutorado não é o término de uma etapa, mas sim o começo. Espero que ainda possamos trabalhar juntos durante muitos anos. Agradeço pela amizade que fizemos e que manteremos.

<sup>&</sup>quot;Well, there is only one mind expanding drug this man enjoys, and that's called school." – Sheldon Cooper, The Big Bang Theory.

#### **RESUMO**

Nesta tese, o disparador Schmitt (ou Schmitt trigger) CMOS clássico (ST) operando em inversão fraca é analisado. A transferência de tensão DC completa é determinada, incluindo expressões analíticas para as tensões dos nós internos. A transferência de tensão DC resultante do ST apresenta um comportamento contínuo mesmo na presenca da histerese. Nesse caso, a característica da tensão de saída entre os limites da histerese é formada por um segmento metaestável, que pode ser explicado em termos das resistências negativas dos subcircuitos NMOS e PMOS do ST. A tensão mínima para o aparecimento da histerese é determinada fazendo-se a análise de pequenos sinais. A análise de pequenos sinais também é utilizada para a estimativa da largura do laco de histerese. É mostrado que a histerese não aparece para tensões de alimentação menores que 75 mV em 300 K. A análise do ST operando como amplificador também foi feita. A razão ótima dos transistores foi determinada com o objetivo de se maximizar o ganho de tensão. A comparação do disparador Schmitt com o inversor CMOS convencional destaca as vantagens e desvantagens de cada um para aplicações de ultra-baixa tensão. Também é mostrado que o ST é teoricamente capaz de operar (com ganho de tensão absoluto ≥1) com uma tensão de alimentação tão baixa quanto 31.5 mV, a qual é menor do que o conhecido limite prévio de 36 mV, para o inversor convencional. Como amplificador, o ST possui ganho de tensão absoluto consideravelmente maior que o inversor convencional na mesma tensão de alimentação. Três circuitos integrados foram projetados e fabricados para estudar o comportamento do ST com tensões de alimentação entre 50 mV e 1000 mV.

**Palavras-chave:** Schmitt trigger. Disparador Schmitt. Ultra-Baixa Tensão. Inversão Fraca. Ultra-Baixa Potência. Inversor CMOS.

#### RESUMO EXPANDIDO

## 1 INTRODUÇÃO

Nos últimos anos, desenvolvimentos significativos direcionados a ultra-baixa tensão foram feitos, com foco principal em aplicações autônomas que dependem de mini ou micro baterias ou que captam a energia do meio ambiente. Tais fontes de energia incluem sinais de radiofrequência, vibradores mecânicos, geradores termoelétricos (TEG), células de combustível de glicose e células fotovoltaicas. Ao mesmo tempo, avanços contínuos na eletrônica em geral, com mais e melhores funcionalidades, permitiram um aumento tremendo em diversos tipos de equipamentos, incluindo sistemas para comunicação, processamento da informação, entretenimento, computação ubíqua, redes de sensores e sistemas médicos.

Fontes ambientais de energia (energy harvesting) representam uma importante fonte de potência. No entanto, o nível de tensão disponível é muito baixo, geralmente em torno de 100 mV. Por exemplo, geradores termoelétricos, que dependem da diferença de temperatura entre o corpo e o ambiente, fornecem uma tensão entre 50 mV e 75 mV, na faixa de 1-3 K. Células fotovoltaicas fornecem centenas de milivolts em ambientes escuros. E, finalmente, uma fonte interessante de energia é proveniente das árvores, focando em aplicações de monitoramento climático e da vida selvagem. A tensão disponível é devida a diferença de pH entre o caule da árvore e o solo.

Uma vez que a tensão disponível é extremamente baixa, os métodos convencionais para alcançar alto ganho de tensão não são apropriados devido à dificuldade de impor a saturação aos transistores. Uma técnica interessante para minimizar esse problema é o uso de realimentação positiva para aumentar o ganho do amplificador. Nessa tese, optamos pela utilização da realimentação positiva presente no disparador Schmitt (Schmitt *trigger*) para se obter um amplificador de alto ganho.

A operação de circuitos digitais CMOS com tensão em torno de 500 mV, ou abaixo disso, força os transistores operarem no regime de inversão fraca ou sublimiar. Esse regime é caracterizado pela relação exponencial entre correntes e tensões dos terminais do transistor.

Diversas aplicações foram desenvolvidas com o objetivo de se minimizar a tensão de alimentação dos circuitos como, por exemplo, um circuito digital operando com  $V_{DD}=4~kT/q~(=103~{\rm mV}~a~300~{\rm K})$ , cadeias de 1000 inversores alimentado com 50 mV, um filtro 8x8 tipo

FIR funcionando com alimentação de 85 mV, memórias SRAM baseadas no disparador Schmitt (ST) funcionais até o limite de 150 mV e, finalmente, um multiplicador 8x8 baseado em estruturas derivadas do disparador Schmitt operando com alimentação de 62 mV. Esta última aplicação inspirou o desenvolvimento desta tese.

#### 2 OBJETIVO

Embora alguns autores afirmem que a cascata de 4 transistores entre alimentação e terra presente no disparador Schmitt clássico não seja apropriado para aplicações de ultra-baixa tensão, ele tem sido empregado como o elemento principal em diversos circuitos de ultra-baixa tensão. O disparador Schmitt clássico é um dos circuitos mais úteis tanto para aplicações digitais quanto analógicas. Analisando o circuito, os transistores de realimentação funcionam como uma fonte de corrente controlada por tensão para os nós intermediários. Nesse sentido, a cascata de 4 transistores é de fundamental importância para o funcionamento do circuito.Além disso, a cascata de transistores já foi utilizada para redução das correntes de fuga.

O disparador Schmitt foi analisado extensivamente em inversão forte. Entretanto, em inversão fraca somente alguns estudos parciais foram realizados, como por exemplo, circuitos lógicos baseados no disparador Schmitt, com o objetivo de se maximizar a razão entre a corrente dos transistores ligados e desligados.

Esta tese tem como objetivo a completa análise do disparador Schmitt operando em inversão fraca. O comportamento estático do disparador Schmitt é analisado em profundidade, são determinadas as tensões nodais, as dimensões ótimas dos transistores que maximiza o ganho quando funcionando como amplificador são calculadas, é explicada a histerese, com comprovações dos resultados através de medidas em circuitos projetados e fabricados especialmente com esses objetivos.

#### 3 RESULTADOS

Teoricamente os inversores CMOS podem funcionar até o limite de 36 mV (em 300K) de tensão de alimentação. Porém, resultados analíticos mostram que o disparador Schmitt otimizado pode funcionar com uma tensão de alimentação de até 31.5 mV (em 300 K), representando um novo limite para circuitos de ultra-baixa tensão.

Se comparado com o inversor convencional CMOS, o ST tem muitas vantagens para aplicações de ultra-baixa tensão. A primeira é que a presença de histerese resulta num circuito comparador de dois níveis com boa eficiência na presença de ruído. Ao mesmo tempo, seu consumo de potência é consideravelmente menor que comparadores baseados em amplificadores operacionais.

A segunda vantagem é que o ganho de tensão do ST é muito maior do que o do inversor convencional quando não há histerese. Entretanto, a desvantagem do ST é que a área ocupada pelo ST é grande, o que resulta em uma frequência de operação menor.

Nos dois casos quando há e quando não há histerese, a margem de ruído estático do ST é maior do que a do inversor convencional. Adicionalmente, o ST é menos susceptível a variações dos parâmetros tecnológicos e de temperatura. Esses dois fatos permitem que o ST seja operacional para tensões de alimentação extremamente baixas.

#### **ABSTRACT**

In this thesis, the classical CMOS Schmitt trigger (ST) operating in weak inversion is analyzed. The complete DC voltage transfer characteristic is determined, including analytical expressions for the internal node voltage. The resulting voltage transfer characteristic of the ST presents a continuous output behavior even when hysteresis is present. In this case, the output voltage characteristic between the hysteresis limits is formed by a metastable segment, which can be explained in terms of the negative resistance of the NMOS and PMOS subcircuits of the ST. The minimum supply voltage at which hysteresis appears is determined carrying out small-signal analysis, which is also used to estimate the hysteresis width. It is shown that hysteresis does not appear for supply voltages lower than 75 mV at 300 K. The analysis of the ST operating as a voltage amplifier was also carried out. Optimum transistor ratios were determined aiming at voltage gain maximization. The comparison of the ST with the standard CMOS inverter highlights the relative benefits and drawbacks of each one in ULV applications. It is also shown that the ST is theoretically capable of operating (voltage gain  $\geq 1$ ) at a supply voltage as low as 31.5 mV, which is lower than the well-known limit of 36 mV, for the standard CMOS inverter. As an amplifier, the ST shows considerable higher absolute voltage gains than those showed by the conventional inverter at the same supply voltages. Three test chips were designed and fabricated to study the operation of the ST at supply voltages between 50 mV and 1000 mV.

**Keywords**: Schmitt trigger. Ultralow Voltage. Subthreshold Operation. Ultralow Power. CMOS Inverter.

## **CONTENTS**

| 1 INTRODUCTION25                                                                           |

|--------------------------------------------------------------------------------------------|

| 1.1 CIRCUITS WITH FEEDBACK27                                                               |

| 1.2 LOGIC CIRCUITS FOR ULTRALOW VOLTAGE OPERATION29                                        |

| 1.3 ULTRALOW VOLTAGE APPLICATIONS32                                                        |

| 1.4 SCHMITT TRIGGER ARCHITECTURES34                                                        |

| 2 SCHMITT TRIGGER CONVENTIONAL OPERATION 39                                                |

| 2.1 WEAK INVERSION OPERATION                                                               |

| 2.2 CALCULATION OF THE HYSTERESIS WIDTH61                                                  |

| 2.3 SIMULATION AND EXPERIMENTAL RESULTS 65                                                 |

| 3 OPERATION OF THE SCHMITT TRIGGER AS AN ULTRALOW-VOLTAGE AMPLIFIER                        |

| 3.1 OPTIMUM TRANSISTOR RATIOS                                                              |

| 4 THE SCHMITT TRIGGER AS AN ULTRALOW-VOLTAGE LOGIC INVERTER                                |

| 4.1 THE 6-TRANSISTOR SCHMITT TRIGGER AS A LOGIC INVERTER: STATIC AND DYNAMIC ANALYSIS      |

| 4.2 LOGIC FAMILIES WITH THE SCHMITT TRIGGER 101                                            |

| 4.3 RING OSCILLATOR WITH THE SCHMITT TRIGGER 105                                           |

| 5 CONCLUSIONS AND FUTURE WORK109                                                           |

| 5.1 CONCLUSIONS                                                                            |

| 5.2 FUTURE WORK                                                                            |

| APPENDIX A – SCHMITT TRIGGER VOLTAGE TRANSFER CHARACTERISTIC113                            |

| APPENDIX B - THE VOLTAGE TRANSFER CHARACTERISTIC AS A 4 <sup>TH</sup> DEGREE EQUATION117   |

| APPENDIX C – DERIVATION OF THE OUTPUT STABLE POINTS OF THE SCHMITT TRIGGER-BASED LATCH 121 |

| APPENDIX D – TRANSCONDUCTANCES OF THE SCHMIT<br>TRIGGER12               |   |

|-------------------------------------------------------------------------|---|

| D.1 WEAK INVERSION12                                                    | 5 |

| D.2 STRONG INVERSION12                                                  | 6 |

| APPENDIX E – HYSTERESIS WIDTH IN MODERATE AN STRONG INVERSION REGIMES12 |   |

| E.1 STRONG INVERSION12                                                  | 9 |

| E.2 MODERATE INVERSION13                                                | 0 |

| APPENDIX F – DESIGNED CHIPS13                                           | 1 |

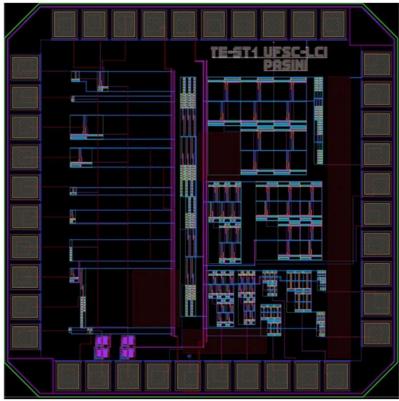

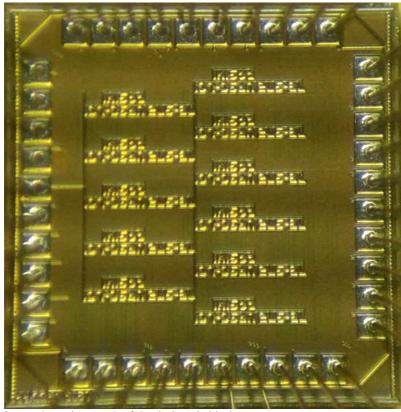

| F.1 DESIGNED CHIP #113                                                  | 1 |

| F.2 DESIGNED CHIP #213                                                  | 3 |

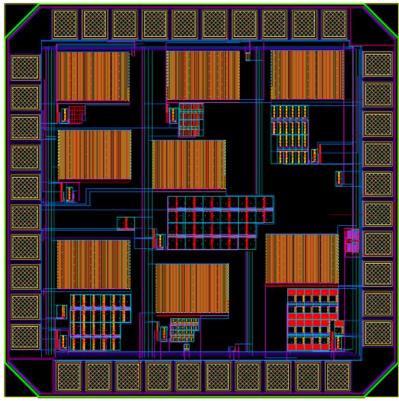

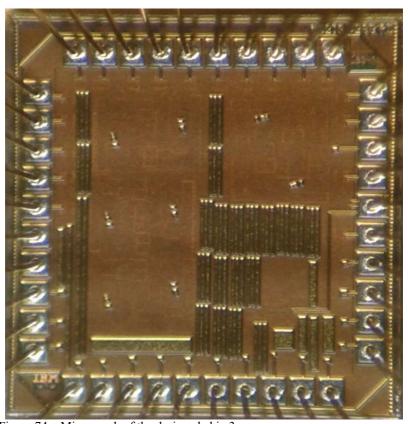

| F.3 DESIGNED CHIP #313                                                  | 5 |

| APPENDIX G – SCHMITT TRIGGER RISE AND FALL TIME13                       |   |

| APPENDIX H – PUBLICATIONS14                                             | 1 |

| REFERENCES14                                                            | 3 |

## LIST OF FIGURES

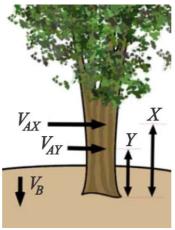

| Figure 1 – Energy harvested from a tree, measured at $V_{AX}$ or $V_{AY}$ , away $X$ or $Y$ from the reference voltage $V_B$ . From [10]26                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

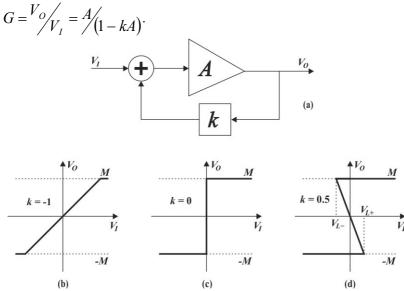

| Figure 2 – (a) Basic structure of a feedback circuit; transfer characteristic of a feedback circuit with (b) $k = -1$ ; (c) $k = 0$ ; (d) $k = 0.5$ . From [24]28                                                                                                 |

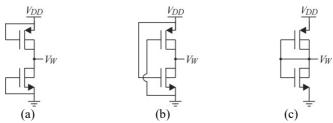

| Figure 3 – CMOS inverter with body bias                                                                                                                                                                                                                           |

| Figure 4 $-$ Body-bias generators that: (a) equalizes off currents [36]; (b) equalizes on currents [35]; (c) centralizes the VTC of the inverter [35]31                                                                                                           |

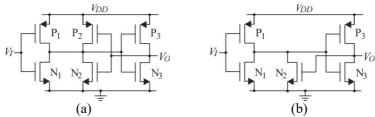

| Figure 5 – Schmitt trigger buffer with parallel association of transistors: (a) latch circuit with inverters [49]; (b) NMOS network parallel association [51]35                                                                                                   |

| $Figure\ 6-Schmitt\ trigger\ buffer\ with\ different\ trip\ point\ inverters\ [53]35$                                                                                                                                                                             |

| Figure 7 – Schmitt trigger for ULV [54] with; (a) dynamic body-biasing; (b) cross-coupled inverters with body-biasing                                                                                                                                             |

| Figure 8 – Classical 6-transistor Schmitt trigger inverter [58]37                                                                                                                                                                                                 |

| $Figure\ 9-Currents\ and\ voltages\ in\ the\ classical\ 6-transistor\ Schmitt\ trigger39$                                                                                                                                                                         |

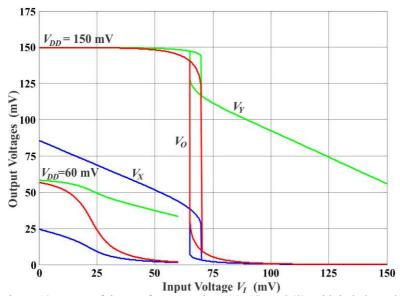

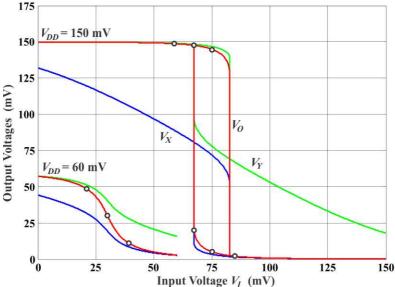

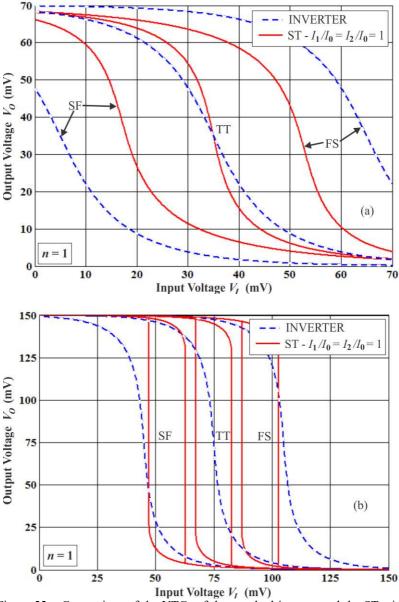

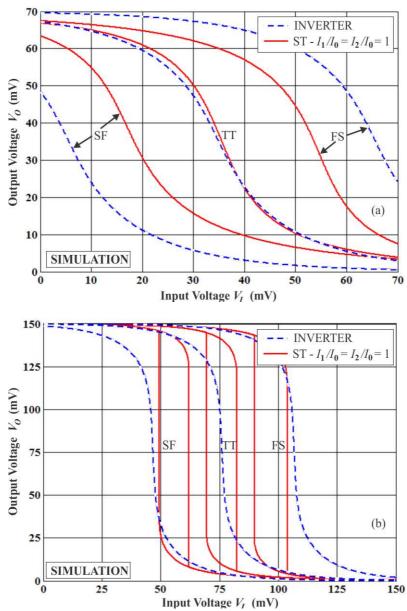

| Figure 10 – VTC of the ST, from equations (5), (6), and (8), with imbalanced p- and n- circuits for $V_{DD}=60$ mV and 150 mV, with $I_{N0}=3$ nA, $I_{N1}=1$ nA, $I_{N2}=1$ nA, $I_{P0}=1.5$ nA, $I_{P1}=0.5$ nA, $I_{N2}=0.5$ nA, $I_{N}=1.3$ , and $I_{N}=1.2$ |

| Figure 11 – VTC of the ST, obtained from equations (9)-(11), with balanced p-and n- circuits for $V_{DD}=60~\mathrm{mV}$ and 150 mV43                                                                                                                             |

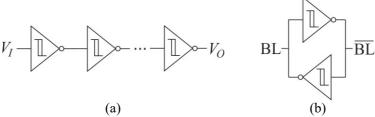

| Figure 12 – (a) Odd number of cascaded STs; (b) ST Latch44                                                                                                                                                                                                        |

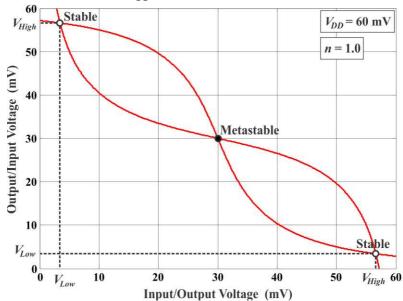

| Figure 13 – Butterfly plot of the Schmitt trigger for $V_{DD}$ = 60 mV, $I_0 = I_1 = I_2$ , and $n$ =1, used to define $V_{Low}$ and $V_{High}$ output stable points of the ST-based latch                                                                        |

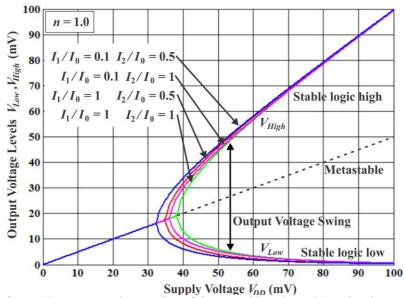

| Figure 14 – Output voltage swing of the ST, with $I_1/I_0=0.1$ and $I_1/I_0=1$ , $I_2/I_0=0.5$ and $I_2/I_0=1$ , for $n=1.0$ , as a function of the supply voltage46                                                                                              |

| Figure 15 – Output voltage swing of the ST, with $I_1/I_0=0.1$ and $I_1/I_0=1$ , $I_2/I_0=0.5$ and $I_2/I_0=1$ , for $n=1.3$ , as a function of the supply voltage46                                                                                              |

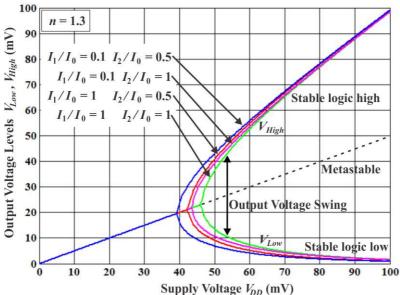

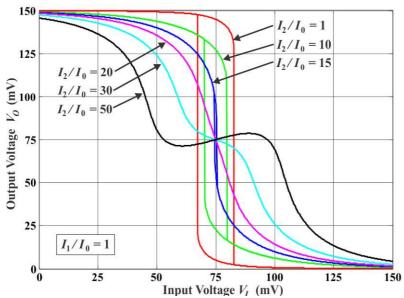

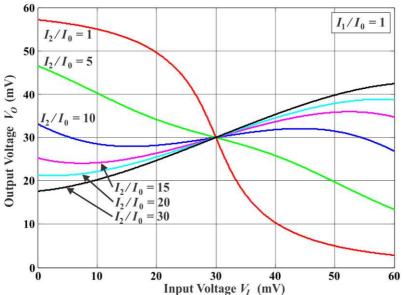

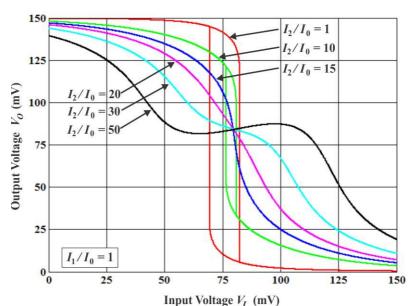

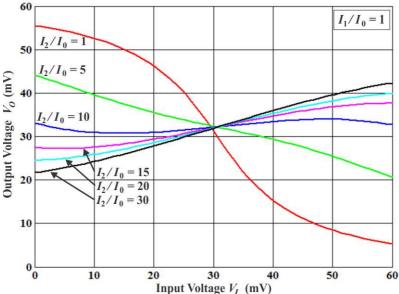

| Figure 16 – VTC of the ST, obtained from equations (9)-(11), with $I_1/I_0$ =1 and $I_2/I_0$ from 1 to 50, for $V_{DD}$ = 150 mV48                                                                                                                                |

| Figure 17 – VTC of the ST, obtained from equations (9)-(11), with $I_1/I_0$ =1 and $I_2/I_0$ from 1 to 30, for $V_{DD}$ = 60 mV48                                                                                                                                 |

| Figure 18 – VTC of the ST, obtained from simulation in 180 nm technology, with $I_1/I_0=1$ and $I_2/I_0$ from 1 to 50, for $V_{DD}=150$ mV49                                                                                                                      |

| Figure 19 – VTC of the ST, obtained from simulation in 180 nm technology, with $I_1/I_0=1$ and $I_2/I_0$ from 1 to 30, for $V_{DD}=60$ mV49                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 20 – ST split into PMOS and NMOS networks50                                                                                                                                                                                                               |

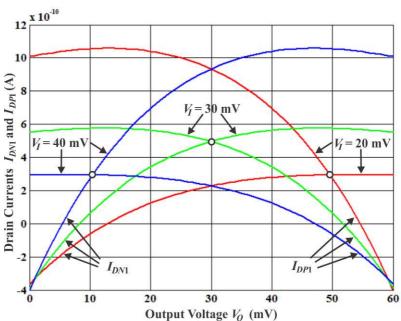

| Figure 21 – Drain currents of $N_1$ and $P_1$ in terms of the output voltage, $V_O$ , for different input voltages, $V_I$ , with $I_0 = I_1 = I_2 = 1$ nA and $V_{DD} = 60$ mV51                                                                                 |

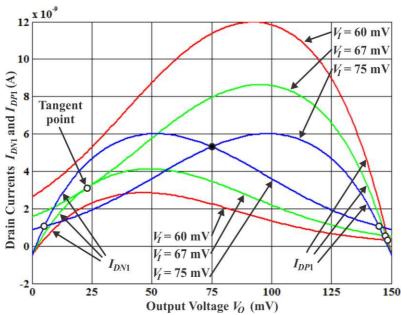

| Figure 22 – Drain currents of $N_1$ and $P_1$ in terms of the output voltage, $V_O$ , for different input voltages, $V_I$ , with $I_0 = I_1 = I_2 = 1$ nA and $V_{DD} = 150$ mV52                                                                                |

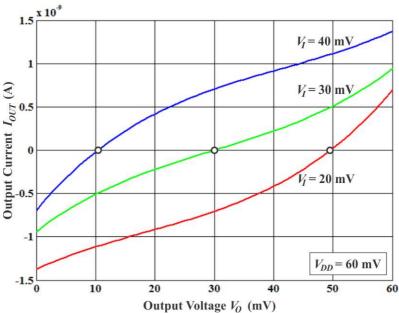

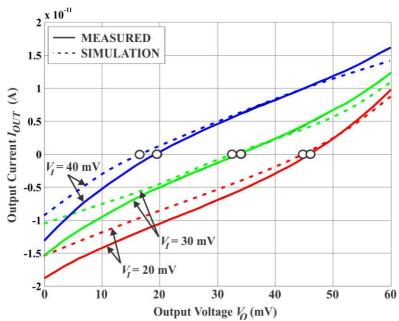

| Figure 23 – Output current, $I_{OUT}$ , as a function of the output voltage, $V_O$ , for $V_I = 20 \text{ mV}$ , 30 mV, and 40 mV, with $I_0 = I_1 = I_2 = 1 \text{ nA}$ , $n = 1$ , and $V_{DD} = 60 \text{ mV}$ . 53                                           |

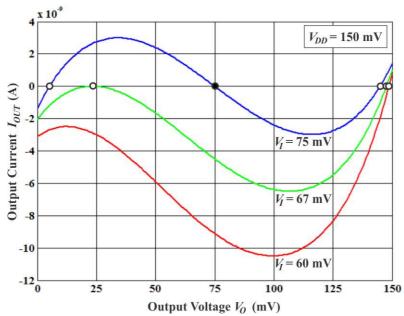

| Figure 24 – Output current, $I_{OUT}$ , as a function of the output voltage, $V_O$ , for $V_I = 60$ mV, 67 mV, and 75 mV, with $I_0 = I_1 = I_2 = 1$ nA, $n = 1$ , and $V_{DD} = 150$ mV.                                                                        |

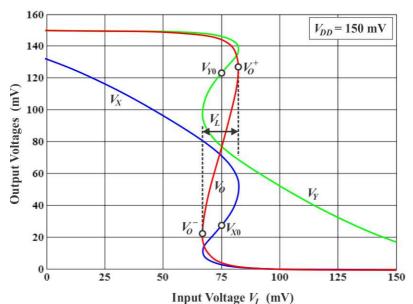

| Figure 25 – "Z" curve formed by both stable and metastable points for $V_{DD}$ = 150 mV, $n = 1$ , and $I_1/I_0 = I_2/I_0 = 1$ 55                                                                                                                                |

| Figure 26 – Small-signal MOSFET model ( $v_b = 0$ )55                                                                                                                                                                                                            |

| Figure 27 – ST small-signal model                                                                                                                                                                                                                                |

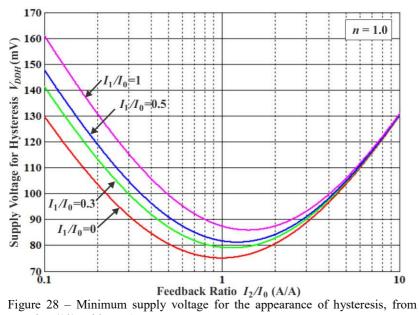

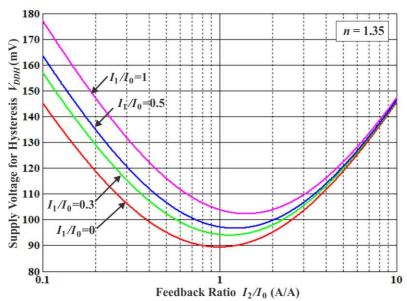

| Figure $28$ – Minimum supply voltage for the appearance of hysteresis, from equation (18), with $n = 1$ 60                                                                                                                                                       |

| Figure 29 – Minimum supply voltage for the appearance of hysteresis, from equation (18), with $n = 1.35$ 60                                                                                                                                                      |

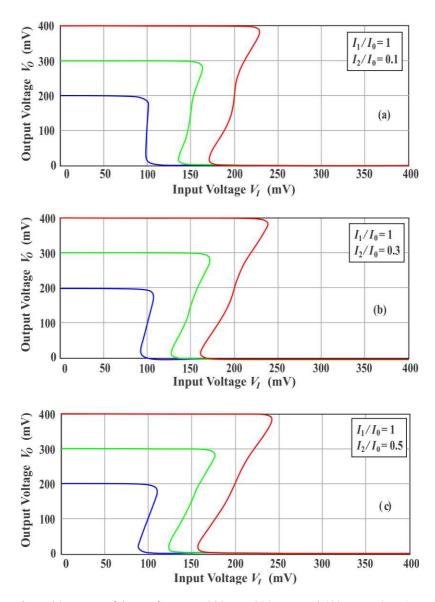

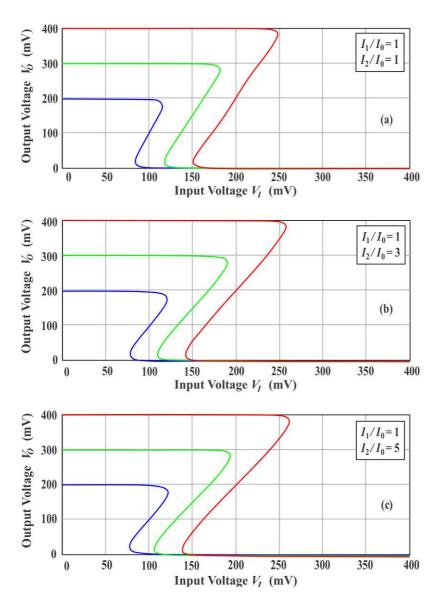

| Figure 30 – VTC of the ST for $V_{DD}$ = 200 mV, 300 mV, and 400 mV, $I_1/I_0$ = 1.<br>Low feedback: (a) $I_2/I_0$ = 0.1; (b) $I_2/I_0$ = 0.3; (c) $I_2/I_0$ = 0.563                                                                                             |

| Figure 31 – VTC of the ST for $V_{DD} = 200 \text{ mV}$ , 300 mV, and 400 mV, $I_1/I_0 = 1$ .<br>High feedback: (a) $I_2/I_0 = 1$ ; (b) $I_2/I_0 = 3$ ; (c) $I_2/I_0 = 5$ 64                                                                                     |

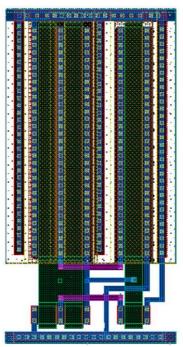

| Figure 32 – Layout of the ST with $I_1/I_0 = I_2/I_0 = 1$ , where $(W/L)_{P0} = (W/L)_{P1} = (W/L)_{P2} = 14 \ \mu \text{m}/1.08 \ \mu \text{m}$ and $(W/L)_{N0} = (W/L)_{N1} = (W/L)_{N2} = 1.08 \ \mu \text{m}/1.08 \ \mu \text{m}$                            |

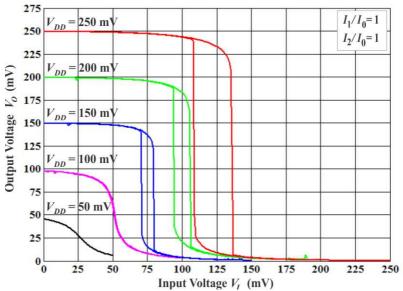

| Figure 33 – Measured VTCs of the ST with $I_1/I_0 = I_2/I_0 = 1$ , for $V_{DD}$ between 50 mV and 250 mV67                                                                                                                                                       |

| Figure 34 – Measured output current, $I_{OUT}$ , as a function of the output voltage, $V_O$ , for $V_I = 20$ mV, 30 mV, and 40 mV, for $V_{DD} = 60$ mV. Open circles are associated with $I_{OUT} = 0$ A                                                        |

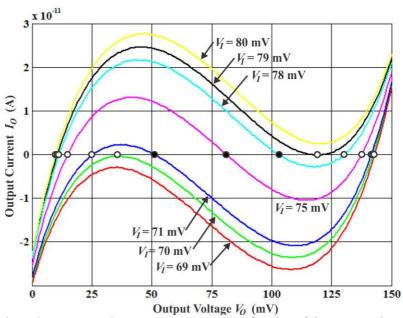

| Figure 35 – Measured output current, $I_{OUT}$ , as a function of the output voltage, $V_O$ , for $V_I = 69$ mV, 70 mV, 71 mV, 75 mV, 78 mV, 79 mV, and 80 mV, for $V_{DD} = 150$ mV. Open circles are stable points, while closed circles are metastable points |

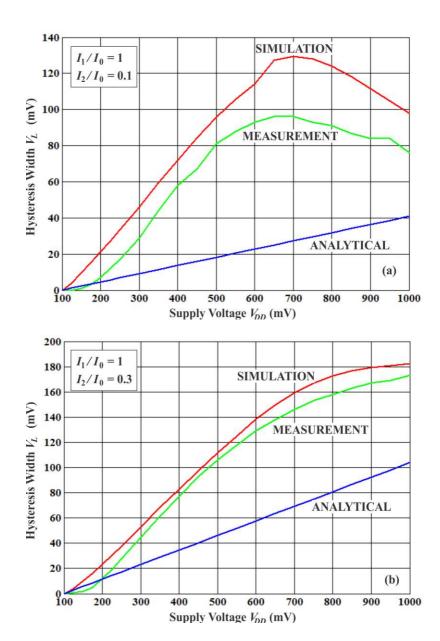

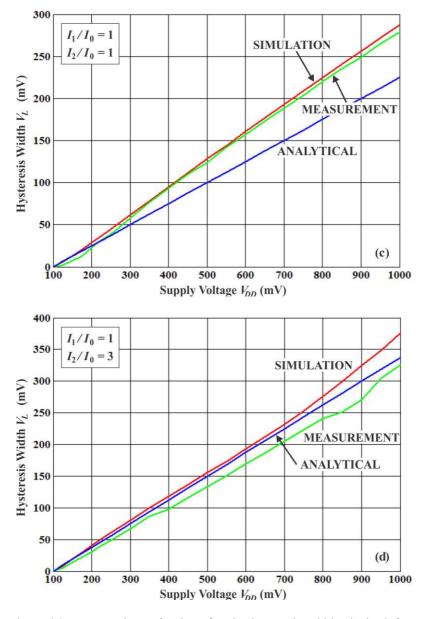

| Figure 36 – Comparison of values for the hysteresis width obtained from measurements, simulations and analytical expression, eq. (30), with $I_1/I_0 = 1$ , and (a) $I_2/I_0 = 0.1$ ; (b) $I_2/I_0 = 0.3$ ; (c) $I_2/I_0 = 1$ ; and (d) $I_2/I_0 = 3$ 72 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

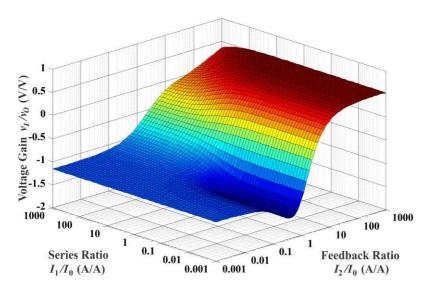

| Figure 37 – Small-signal voltage gain of the ST for $V_{DD} = 40$ mV, $n = 1$ 74                                                                                                                                                                         |

| Figure 38 – Small-signal voltage gain of the ST for $V_{DD}$ = 50 mV, $n$ = 174                                                                                                                                                                          |

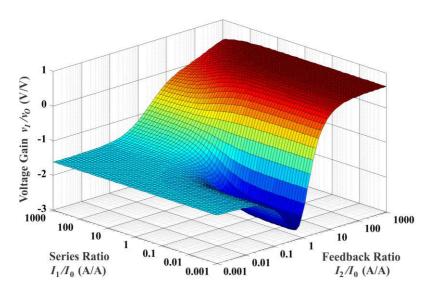

| Figure 39 – Small-signal voltage gain of the ST for $V_{DD}$ = 60 mV, $n$ = 175                                                                                                                                                                          |

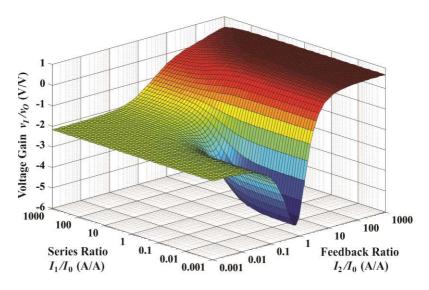

| Figure 40 – Small-signal voltage gain of the ST for $V_{DD}$ = 70 mV, $n$ = 175                                                                                                                                                                          |

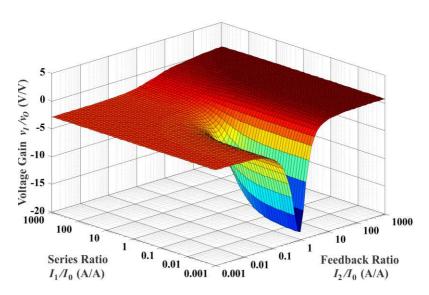

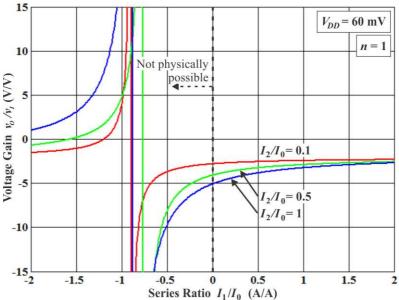

| Figure 41 – Small-signal voltage gain of the ST for $V_{DD}$ = 60 mV, $n$ = 1, for different $I_2/I_0$ ratios, as a function of the $I_1/I_0$ ratio                                                                                                      |

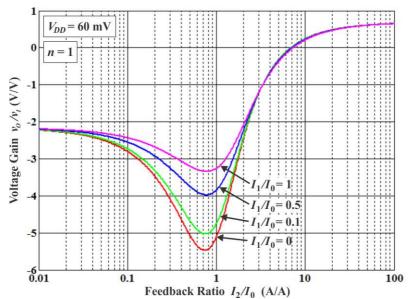

| Figure 42 – Small-signal voltage gain of the ST for $V_{DD}$ = 60 mV, $n$ = 1, for different $I_1/I_0$ ratios, as a function of the $I_2/I_0$ ratio                                                                                                      |

| Figure 43 – Conventional CMOS inverter                                                                                                                                                                                                                   |

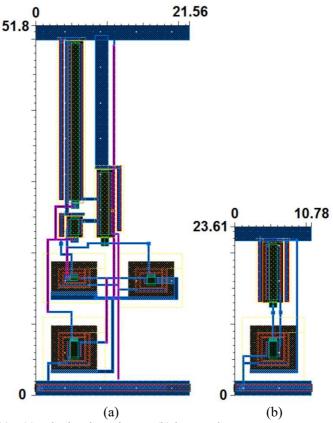

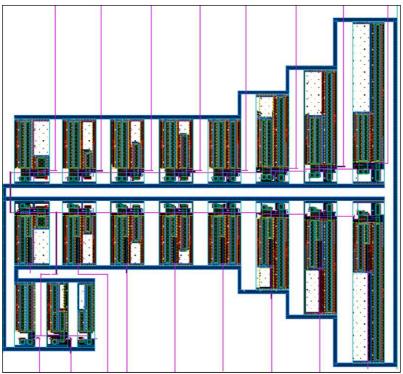

| Figure 44 – (a) Schmitt trigger layout; (b) inverter layout83                                                                                                                                                                                            |

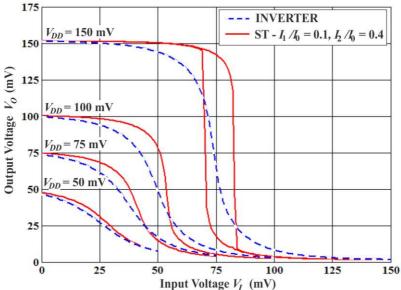

| Figure 45 – Measured VTC comparison of the ST and the inverter for $V_{DD}$ = 50 mV, 75 mV, 100 mV, and 150 mV84                                                                                                                                         |

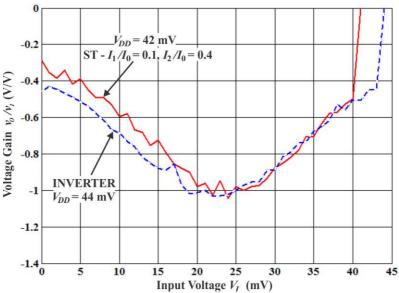

| Figure 46 – Measured voltage gain transfer, for minimum supply voltage for the ST and the inverter in chip sample number 5                                                                                                                               |

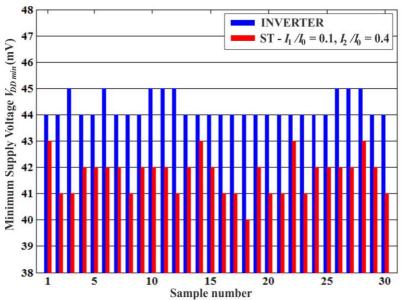

| Figure 47 – Measured minimum supply voltage of both the ST and the inverter on 30 samples                                                                                                                                                                |

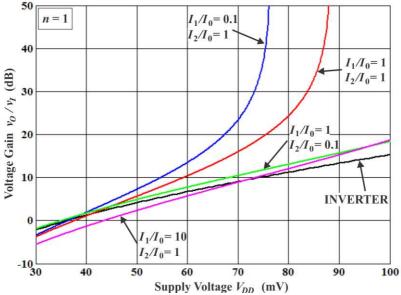

| Figure $48$ – Comparison of the gains of the standard inverter and the Schmitt trigger, from analytical expressions, with different transistor strength ratios86                                                                                         |

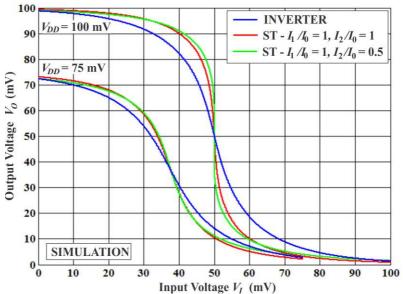

| Figure 49 – Simulated VTCs of the ST and the inverter for $V_{DD}$ = 75 mV and $V_{DD}$ = 100 mV in a 180 nm technology87                                                                                                                                |

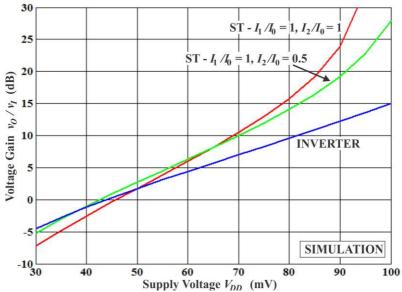

| Figure 50 – Simulated voltage gains obtained for the inverter and STs with $I_2/I_0$ = 0.5 and $I_2/I_0$ = 1, and $I_1/I_0$ = 189                                                                                                                        |

| $Figure \ 51-Layout \ of \ the \ fabricated \ Schmitt \ triggers \ and \ inverter90$                                                                                                                                                                     |

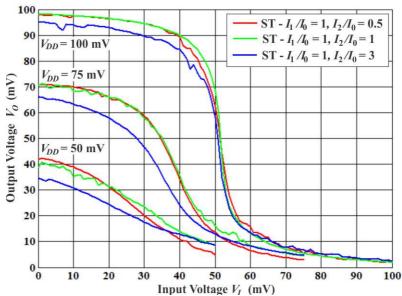

| Figure 52 – Measured VTCs of the ST with $I_1/I_0 = 1$ and $I_2/I_0 = 0.5$ , 1, and 3, for $V_{DD} = 50$ mV, 75mV, and 100 mV91                                                                                                                          |

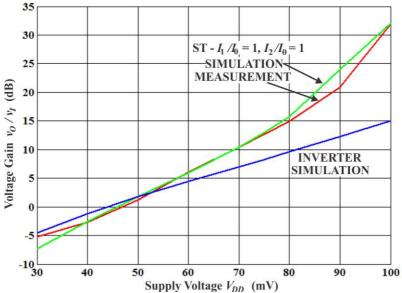

| Figure 53 – Comparison between the voltage gain of a simulated inverter, and both simulated and measured values for a ST with $I_1/I_0 = I_2/I_0 = 1$ 92                                                                                                 |

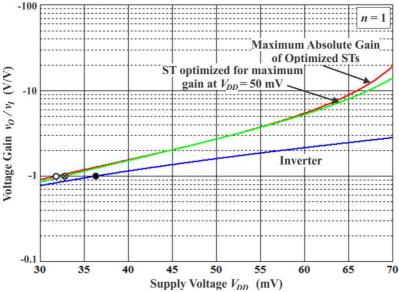

| Figure 54 – Comparison of the maximum absolute gains of the Schmitt trigger optimized for maximum gain at any supply voltage, the Schmitt trigger optimized for 50 mV, and the conventional inverter93                                                   |

| Figure 55 – Comparison of the VTCs of the standard inverter and the ST with $I_1/I_0 = I_2/I_0 = 1$ , from analytical expressions, under a $\pm 30$ mV variation in the threshold voltage for: (a) $V_{DD} = 70$ mV; (b) $V_{DD} = 150$ mV95 |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Figure 56 – Comparison of the VTCs of the standard inverter and the ST with $I_1/I_0 = I_2/I_0 = 1$ , from simulation, for SF, TT, and FS corners for: (a) $V_{DD} = 70$ mV; (b) $V_{DD} = 150$ mV96                                         |  |

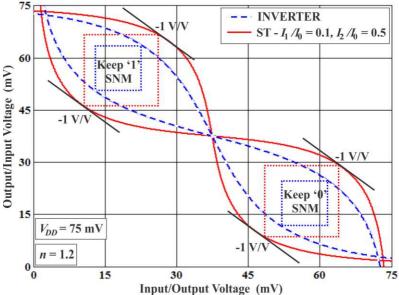

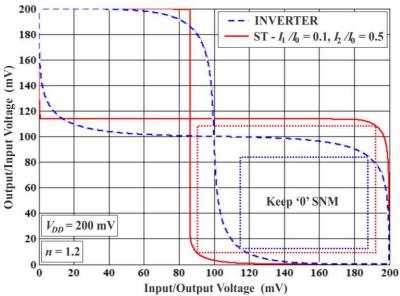

| Figure 57 – Butterfly plots for the "Keep '1' SNM" and "Keep '0' SNM" states of the Schmitt trigger ( $I_1/I_0 = 0.1$ , $I_2/I_0 = 0.5$ ) and the conventional inverter for $V_{DD} = 75$ mV, $n = 1.2$                                      |  |

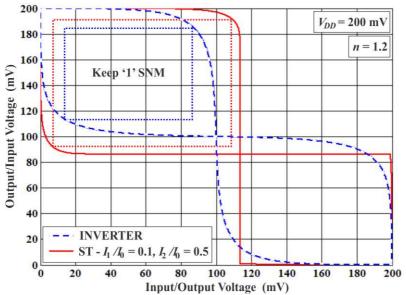

| Figure 58 – Butterfly plots for the "Keep '1' SNM" state of the Schmitt trigger $(I_1/I_0 = 0.1, I_2/I_0 = 0.5)$ and the conventional inverter for $V_{DD} = 200$ mV, $n = 1.2$ .                                                            |  |

| Figure 59 – Butterfly plots for the "Keep '0' SNM" state of the Schmitt trigger $(I_1/I_0 = 0.1, I_2/I_0 = 0.5)$ and the conventional inverter for $V_{DD} = 200$ mV, $n = 1.2$ .                                                            |  |

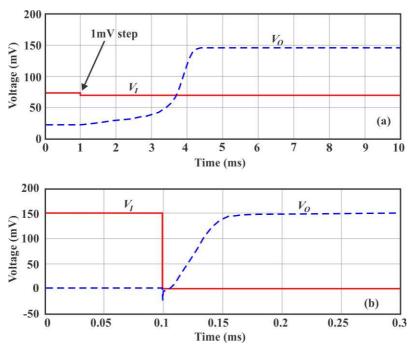

| Figure 60 – Simulated transient time of the ST with $I_1/I_0 = I_2/I_0 = 1$ , for $V_{DD} = 150$ mV, for: (a) 1 mV input step; (b) 150 mV input step100                                                                                      |  |

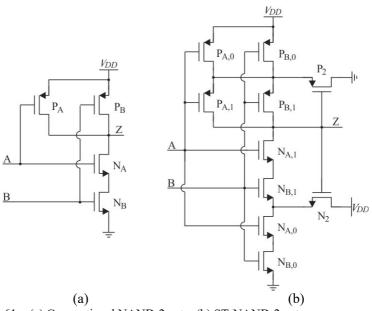

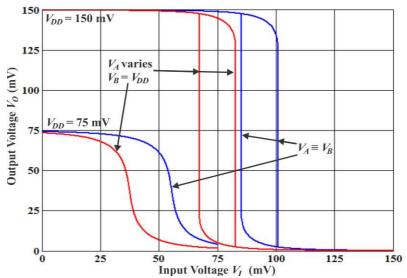

| Figure 61 – (a) Conventional NAND-2 gate; (b) ST-NAND-2 gate101                                                                                                                                                                              |  |

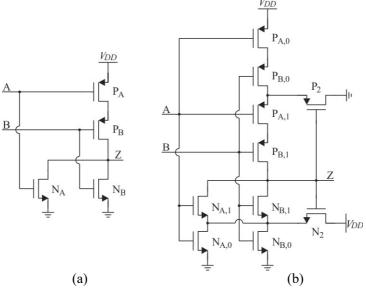

| Figure 62 – (a) Conventional NOR-2 gate; (b) ST-NOR-2 gate102                                                                                                                                                                                |  |

| Figure 63 – ST-NAND-2 equivalent circuits when (a) only one input varies; (b) both inputs vary together                                                                                                                                      |  |

| Figure 64 – ST-NAND-2 VTC when only one input varies and when both inputs vary together, from analytical expressions, for $V_{DD} = 75$ mV and 150 mV, and $n = 1$                                                                           |  |

| Figure 65 – ST-NAND-3 VTC when only one input varies, and when two and three inputs vary together, from analytical expressions, for $V_{DD} = 75 \text{ mV}$ , $n = 1$                                                                       |  |

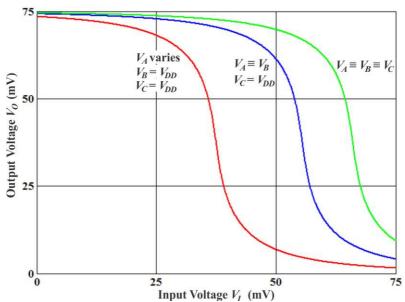

| Figure 66 – 3-stage ring oscillators: (a) ST-based; (b) inverter-based105                                                                                                                                                                    |  |

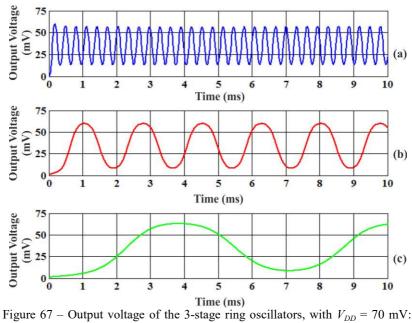

| Figure 67 – Output voltage of the 3-stage ring oscillators, with $V_{DD} = 70$ mV: (a) inverter-based; (b) ST-based $I_1/I_0 = I_2/I_0 = 1$ ; (c) ST-based $I_1/I_0 = 0.1$ , $I_2/I_0 = 1$ .                                                 |  |

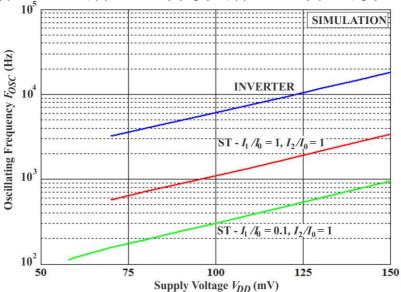

| Figure 68 – Comparison between the oscillation frequencies of the simulated STs and inverter based 3-stage ring oscillators107                                                                                                               |  |

| Figure 69 – Classical 6-transistor Schmitt trigger currents and voltages113                                                                                                                                                                  |  |

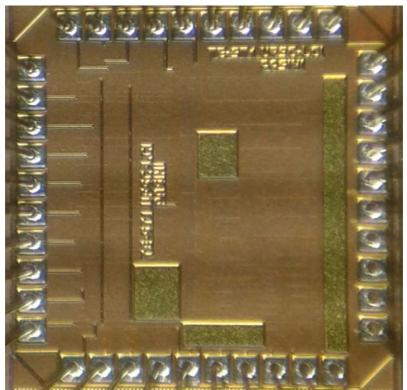

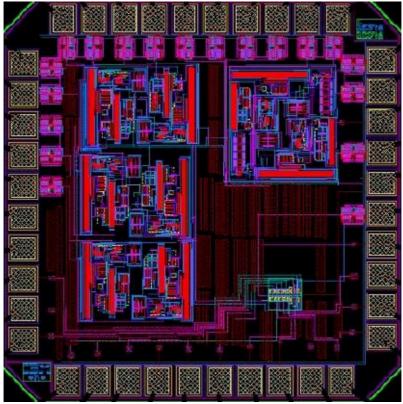

| Figure 70 – Micrograph of the designed chip 1131                                                                                                                                                                                             |  |

| Figure 71 – Layout of the designed chip 1                                                                                                                                                                                                    |  |

| Figure 72 – Micrograph of the designed chip 2.                        | .133 |

|-----------------------------------------------------------------------|------|

| Figure 73 – Layout of the designed chip 2                             | .134 |

| Figure 74 – Micrograph of the designed chip 3.                        | .135 |

| Figure 75 – Layout of the designed chip 3                             | .136 |

| Figure 76 – Layout of the designed Schmitt triggers inside chip 3     | .137 |

| Figure 77 – Schmitt trigger (a) discharge circuit; (b) charge circuit | .139 |

|                                                                       |      |

## LIST OF TABLES

| TABLE I – Output high and low level voltages of the non-symmetrical (see Fig. 27) and symmetrical (Fig. 28) STs for $V_{DD} = 60 \text{ mV}$ |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| TABLE II – Transconductances of the Schmitt trigger for $V_O = V_I = V_{DD}/257$                                                             |

| TABLE III – Optimum values of $I_2/I_0$ for different supply voltages, with $I_1/I_0 = 0$ and $n = 1$                                        |

| TABLE IV – Schmitt trigger and inverter transistor aspect ratios88                                                                           |

| TABLE V – Comparison between the inverter and the optimized Schmitt trigger gain for different supply voltages $(n = 1)$                     |

| TABLE VI – Schmitt trigger and inverter transistor aspect ratios of the 3-stage ring oscillators                                             |

| TABLE VII – Transconductances of the ST in WI for $V_O = V_I = V_{DD}/2$                                                                     |

| TABLE VIII – Transconductances of the ST in SI for $V_O = V_I = V_{DD}/2$                                                                    |

#### LIST OF ABBREVIATIONS

B Bulk terminal

BB Body Bias

BiCMOS Bipolar CMOS

BJT Bipolar Junction Transistor CMOS Complementary MOS

D Drain terminal

DC Direct Current

FBB Forward Body Bias

FDSOI Fully Depleted Silicon on Insulator

FET Field Effect Transistor

FF Fast NMOS and PMOS transistors

FIR Finite Impulse Response

FS Fast NMOS and slow PMOS transistors

G Gate terminal

Ge Germanium

IC Integrated Circuit

IoE Internet of Everything

IoT Internet of Things

ITRS International Roadmap for Semiconductors

KCL Kirchhoff Current Law Line Edge Roughness

NMOS N-type MOST NBB No Body Bias

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOST Metal Oxide Semiconductor Transistor

OP-AMP Operational Amplifier

PDN Pull Down Network

PMOS P-type MOST

PUN Pull Up Network

PUN Pull Up Network

PVT Process, Voltage, and Temperature

RBB Reverse Body Bias

RDF Random Dopant Fluctuations

RO Ring Oscillator

RSCE Reverse Short Channel Effect

S Source terminal

SF Slow NMOS and fast PMOS transistors

Si Silicon

SNM Signal-to-Noise Margin

SoS Silicon-on-sapphire

SRAM Static Random Access Memory SS Slow NMOS and PMOS transistors

ST Schmitt Trigger

TEG Thermo-electric generator

TT Typical NMOS and PMOS threshold voltage

transistors

ULP Ultralow Power ULV Ultralow Voltage

VTC Voltage Transfer Characteristic

VTC<sup>-1</sup> Inverted Voltage Transfer Characteristic

ZBB Zero Body Bias

## LIST OF SYMBOLS

| $2\varepsilon$ | Output voltage swing                                            |

|----------------|-----------------------------------------------------------------|

| Φt             | Thermal voltage                                                 |

| μ              | Carrier mobility                                                |

| $c_{0-4}$      | Coefficients of the 4 <sup>th</sup> degree ST transfer function |

| $C'_{OX}$      | Gate capacitance per unit area                                  |

| $C_O$          | Output capacitance                                              |

| $C_L$          | Load capacitance                                                |

| clk            | Clock signal                                                    |

| $d_{0-4}$      | Coefficients of the ST output voltage swing                     |

| G              | Voltage gain                                                    |

| $g_m$          | Gate transconductance                                           |

| $g_{md}$       | Drain transconductance                                          |

| $g_{ms}$       | Source transconductance                                         |

| I              | Current strength of the transistor                              |

| $i_d$          | Small-signal drain current                                      |

| $I_D$          | Drain current of the transistor                                 |

| $I_{F(R)}$     | Forward (reverse) current                                       |

| $i_{f(r)}$     | Forward (reverse) inversion level                               |

| $I_O$          | Current scaling factor of the transistor                        |

| $I_{ON}$       | On or driving current                                           |

| $I_{OFF}$      | Off or leakage current                                          |

| $I_{SQ}$       | Specific current of the transistor                              |

| k              | Boltzmann constant                                              |

| L              | Transistor length                                               |

| m              | Number of inputs of a digital gate                              |

| n              | Slope factor                                                    |

| N(P)           | N(P)-type transistor                                            |

| q              | Electron charge                                                 |

| $Q$ ' $_{IS}$  | Normalized inversion charge at the source                       |

| $Q'_{IX}$      | Normalized inversion charge along the channel                   |

| S              | Aspect ratio of the transistor                                  |

| T              | Absolute temperature                                            |

| $V_{DD}$       | Positive supply voltage                                         |

| $V_{DDmin}$    | Minimum supply voltage                                          |

| $V_{DB}$       | Drain-bulk voltage                                              |

| $V_{DS}$       | Drain-source voltage                                            |

| $V_{GB}$       | Gate-bulk voltage                                               |

| $V_H$          | High-level voltage                                              |

| $V_I$          | Input voltage                                                   |

|                |                                                                 |

$v_I$  Small-signal input voltage  $V_{IH}$  High-level input voltage  $V_{IL}$  Low-level input voltage

$V_L$  Hysteresis width voltage of the Schmitt trigger  $V_M$  Threshold, trip or transition voltage of the gate

$V_O$  Output voltage

$v_O$  Small-signal output voltage  $V_{OH}$  High-level output voltage  $V_{OL}$  Low-level output voltage

$V_P$  Pinch-off voltage of the transistor

$V_{SB}$  Source-bulk voltage  $V_{T0}$  Threshold voltage  $V_X$  Voltage at node X

$v_X$  Small-signal voltage at node X  $V_W$  Body bias compensation voltage

$V_Y$  Voltage at node Y

$v_Y$  Small-signal voltage at node Y

W Transistor width

#### 1 INTRODUCTION

In recent years, significant developments towards ultralow voltage have been made, mainly focusing on autonomous applications that rely on miniature batteries or that harvest energy from the environment [1],[2]. Such sources of energy include RF signals, mechanical vibrators, body-worn thermo-electric generators (TEG), glucose fuel cells and photovoltaic cells. At the same time, continuous advances in general electronics, with more and better functionalities, allowed tremendous increase in several kinds of equipments, including systems for communication, information processing, entertainment, ubiquitous computing, sensor networks, and medical systems.

In 2009, electronic devices accounted for 15 % of household electricity consumption, and it may double by 2020, and triple by 2030 [3]. Even for those applications that do not rely on batteries but are always connected to the wall plug, any technique which reduces power consumption is welcome. Consequently, not only voltage constrained applications may benefit from ultralow voltage techniques; all electronic devices shall benefit from them, consuming less energy and in a more efficient way. For applications that rely on or need a battery such as implantable devices, hearing-aid devices, or environment sensors, ultralow voltage is required in order to extend battery life and avoid or postpone surgical interventions or trips to places of difficult access such as the middle of a forest. In this sense, Professor Jan Rabaey predicts that in the near future the majority of objects will have a wireless connection, resulting in billions, or even trillions of connected devices. called the sensory swarm [4]. This will be enabled by the pervasive wireless networking and ultralow power technologies. Gartner, Inc. predicts that Internet of Things (IoT), the network of physical objects that contain embedded technology to communicate and sense or interact with their internal states or the external environment and which excludes portable computers, tablets and smart phones, will grow to 26 billion units in 2020 [5]. At the same time, ABI Research states that ultralow power technologies, the key enabler of the Internet of Everything (IoE), will allow 30 billion devices by 2020 [6], following the same trend. All these devices must capture their own energy, once it is just impossible for all of them to use batteries. Moreover, the environment just cannot handle all the quantity of batteries after their disposal.

Ambient energy-harvesting sources represent an important source of power. However, the voltage level available from them is very low,

generally below 100 mV. For example, thermo-electric generators (TEG) based on bismuth telluride, Bi<sub>2</sub>Te<sub>3</sub> [7], that rely on the temperature difference between the human body and the environment, in the range of 1-3 K, sources a voltage between 50 mV and 75 mV [8]. Similarly, photovoltaic cells provide hundreds of milivolts in dark office environments [9]. Finally, an interesting source of energy is available from trees, focusing applications for climatic and wildlife monitoring, as shown in Fig.1. Supplied voltage is due to pH difference between the tissue of the tree (points X or Y above the soil) and the soil (point B), and is in the range of 20 mV to 200 mV [10].

Figure 1 – Energy harvested from a tree, measured at  $V_{AX}$  or  $V_{AY}$ , away X or Y from the reference voltage  $V_B$ . From [10].

As the supply voltage of digital circuits is reduced to extremely low values, in the range of tens of millivolts, the output voltages corresponding to the logic levels '0' and '1' deviates significantly from the supply rails. This situation characterizes ultralow voltage operation [11]. However, this concept is not widely accepted and here we consider ultralow voltage simply the operation of the circuits in the subthreshold regime.

In the ultralow voltage context, DC-DC converters are widely used to convert one voltage level into another in both discrete and integrated circuits (IC). However, these converters suffer from poor efficiency (around 20 % in ultralow voltage regime), may require non-integrated inductors and capacitors and some of them need considerable startup voltages (in the range of 200-700 mV) [10],[12]. Consequently,

it is very interesting to supply digital circuits directly from the input source or through a step down low dropout linear regulator, without the need of a step up converter. The drawback of the linear step down regulators is that they reduce the (already low) voltage available for the digital circuits; so, supplying the circuits directly from the input source is the preferred option.

Now, considering the technologies available in the present and given the dynamics of the semiconductor industry, the commercial off-the-shelf electronics nowadays and in the near future will continue to use CMOS technology. As predicted by the Moore law, to keep costs within acceptable range, CMOS technology is the preferred one or even the mandatory solution for ultralow power and ultralow voltage applications [13],[14]; bulk CMOS technology based on silicon (Si) substrate is the cheapest and most used one. Since ultralow voltage applications do not really respond at high speed, mature bulk CMOS technologies are suitable and preferred in terms of costs [15].

The operation of digital logic and memories in subthreshold regime requires device, circuit and architectural design optimizations, different of those normally used in strong inversion [16]. Circuits that operate in subthreshold regime suffer from low speed. However, these circuits are intended for ultralow power and ultralow voltage applications and not high performance ones [16]. Actually, the most crucial challenges faced by the circuits operating in subthreshold are: degradation of performance, ensure energy efficiency under performance/voltage range, reduction of yield due to process, voltage or temperature (PVT) variations, increased leakage to overall energy budget ratio, large design effort to ensure performance/energy constraints [17]. All these topics are of great importance and have been addressed along the years, even though a lot of research still needs to be done.

#### 1.1 CIRCUITS WITH FEEDBACK

Under extremely low supply voltages, conventional methods for achieving high voltage gain are not appropriate due to the difficulty of imposing that the transistors operate in saturation [18]-[20]. An interesting technique to mitigate this drawback is the use of positive feedback to generate a compensating negative conductance for the purpose of enhancing the amplifier gain [21]-[23]. However, the structures proposed in [21]-[23] rely on the existence of differential signals to generate a negative resistance to compensate the positive

resistance at the output. Generating differential voltages with low supply voltages is not an easy task.

The arrangement of Fig. 2 (a) represents the basic diagram of feedback circuits. A linear amplifier with gain A receives as input the sum of the input voltage and a fraction of the output multiplied by the feedback factor, k. The resulting static gain is given by

Figure 2 – (a) Basic structure of a feedback circuit; transfer characteristic of a feedback circuit with (b) k = -1; (c) k = 0; (d) k = 0.5. From [24].

Figure 2 (b)-(d) shows the input-output transfer characteristic of the circuit of Fig. 2 (a) for different values of the feedback factor [24].

Negative feedback occurs when k < 0. Assuming a high gain linear amplifier  $(A \rightarrow \infty)$ , the circuit operates with a positive gain of -1/k. For k = -1, the circuit operates as a voltage follower (G = 1). The circuit operates as an ideal discriminator when no feedback is present (k = 0); the output assumes positive saturation M when  $V_I > 0$ , and negative saturation -M when  $V_I < 0$ .

Positive feedback occurs when k > 0. Little changes on the input are amplified in a self-supporting loop until the output saturates at either a positive or a negative value. The loop feeds back a voltage of Mk (or -Mk) that must be surpassed by the input voltage, i.e.  $V_I < -Mk$  (or  $V_I > Mk$ ) in order to move the output to the other direction, where it saturates again. The transitions from the two output levels are considerably sharp

for reasonable high supply voltages. Within the hysteresis limits ( $V_{L+}$  and  $V_{L-}$ ), the output has two stable levels and one metastable level, which is prone to move to one of the stable levels. The transition from the metastable level to any of the stable levels is represented by a negative resistance. The transition from one stable output to the other stable output is a dynamic phenomenon [25],[26], not considered in Fig. 2 (a).

In this thesis we have opted to make use of the positive feedback present in the Schmitt trigger to obtain a high gain amplifier.

#### 1.2 LOGIC CIRCUITS FOR ULTRALOW VOLTAGE OPERATION

Different techniques and approaches can be used to implement logic functions in CMOS technology, considering the ease of implementation, robustness, area, density, speed, and power dissipation [13]. However, there is no specific or single solution that solves all these issues at the same time.

Pseudo-NMOS logic working in subthreshold regime was first proposed in [27]. It requires an always on PMOS transistor as an active load, which actually represents the main drawback of this logic family. The logic function is determined by a series/parallel association of NMOS transistors. Although pseudo-NMOS logic exhibits lower delays and lower power-delay product (PDP) if compared to the static CMOS counterpart in subthreshold regime of operation, it is less attractive when total energy per cycle is considered [28]. Also, note that the NMOS transistors that evaluate the logic function are fighting against a single PMOS transistor. If local and global process variations are taken into account, this logic style provides higher output level variability when operating in subthreshold regime, resulting in low yield.

Sub-Domino logic is the Domino logic operating in the subthreshold regime and was proposed in [29] as an alternative for ultralow voltage applications. Sub-Domino logic is a dynamic and dualphase logic in which a clock signal controls the precharge and the evaluate phases. At the precharge phase, the output node can be charged to either a high (logic function is determined by series/parallel array of NMOS transistors) or a low (logic function is determined by series/parallel array of PMOS transistors) level, depending on the circuit topology. However, note that, depending on the input signal pattern, at the precharge phase the output of the gate is charged (or discharged) to immediately be discharged (or charged) at the evaluation phase. Thus, the activity of the output signal can be high, leading to a high

dissipation of energy, if compared to the static logic [30]. The main drawbacks of the Sub-Domino logic are: it requires an inverter at the output in order to allow cascading of the gates, it is highly sensitive to noise [29], and due to the fact that the evaluate phase can be quite long in subthreshold regime of operation, the dynamic node may lose charge because of the leakage currents, resulting in logic errors.

CMOS static logic is the most common logic style in subthreshold regime of operation due to its robustness [31] and simplicity. It requires no clock or differential signals for proper operation, it has good static noise margins, it does not have dynamic nodes, and it can be cascaded very easily. For these reasons, static logic is the best general-purpose option in subthreshold [32] among other available techniques such as the ones presented in the previous paragraphs. The design of static logic gates can be automated with a high degree of confidence.

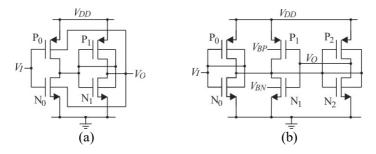

However, as the supply voltage is reduced, the dependence of the performance on PVT variations reduces and degrades the usage of the conventional CMOS static logic gates in subthreshold (with no body bias – NBB, or zero body bias – ZBB), to the same extension of other logic families. For example, a variation in the threshold voltage, which can be in the range of ±30 mV for current technologies, can shift right or left the voltage transfer characteristic (VTC) and, so, degrade the static noise margin (SNM) of the standard inverter. Threshold voltage variation is also responsible for the increase in the minimum operating supply voltage of the SRAMs. To minimize the effects of PVT variations, a number of compensation techniques have been developed, some of which include body-bias (BB) compensation [33]-[35], and tunable supply and body biasing [36] voltages. The idea behind all the compensations techniques is to equalize or tune the currents of the MOSFETs, with the application of a proper bias voltage to the body of each transistor, as shown in Fig. 3. The bias voltage applied to the pchannel transistors,  $V_{BP}$ , and n- channel transistors,  $V_{BN}$ , can be equal or not, depending on the bias voltage generator, design and application.

Figure 3 – CMOS inverter with body bias.

Body-bias compensation techniques can be divided into two groups. The first one is the Forward Body Bias (FBB) technique, which uses bias voltages that lie between the supply rails. The main advantages of FBB are the simplicity to generate the bias voltages and the increase in the maximum operating frequency of the transistor [35]. However, the technique has a stringent drawback: the parasitic sourcebulk and drain-bulk diodes are forward biased, thus increasing power dissipation [35]. FBB is limited to 600-700 mV of supply voltage. The second technique is the Reverse Body Bias (RBB), which uses bias voltages that are higher than the positive supply voltage for the PMOS transistors and lower than the negative supply voltage (generally ground) for the NMOS transistors. Generating the bias voltages for RBB is not simple and may require charge-pumps or other boost converters. The advantages of RBB is that source-bulk and drain-bulk diodes are always reverse biased and the leakage currents of both NMOS and PMOS transistors are reduced, which in turn, reduces the static power dissipation of the logic gate.

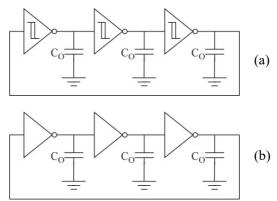

Figure 4 shows three FBB body bias generators; note that the bodies of the transistors are connected to the drains. The bias generator of Fig. 4 (a) generates a voltage  $V_W$  which, applied to the NMOS and PMOS bodies of an identical inverter, will (try to) equalize the off or leakage currents of the NMOS and PMOS transistors [36]. The bias generator of Fig. 4 (b) equalizes the on or driving currents of the transistors [35], and so the rise and fall times of a conventional inverter. Finally, the bias generator of Fig. 4 (c) equalizes the currents when the input voltage is equal to the output voltage [35], i.e., it centralizes the voltage transfer characteristic of the inverter (but does not necessarily equalize the rise and fall times).  $V_W$  is the generated voltage (to be applied to both NMOS and PMOS transistors in these cases).

Figure 4 – Body-bias generators that: (a) equalizes off currents [36]; (b) equalizes on currents [35]; (c) centralizes the VTC of the inverter [35].

Body-biasing can be applied to NAND, NOR and other logic gates as well. Note, however, that body-biasing is not limited to CMOS static logic; it can be used by any other circuit, with proper bias generators in order to reduce the effects of PVT variations.

As already stated, static logic is one of the possible techniques intended for ultralow voltage applications. From the logic families mentioned above, static logic gates are the current trend [32] in ultralow voltage applications. Particularly, static logic gates based on the Schmitt trigger (ST) inverter is a promising approach for ULV. Detailed explanation about the ST architectures will be given in Section 1.4.

#### 1.3 ULTRALOW VOLTAGE APPLICATIONS

The operation of CMOS digital circuits from supply voltages of 500mV or lower forces, in many cases, the transistors to operate in the weak inversion, or subthreshold, regime [37]. This regime is characterized by the exponential relationship between currents and terminal voltages. The design of subthreshold circuits has been focused on obtaining minimum energy per logic operation [38], but there are applications for which a reduction of the supply voltage below the value that results in the minimum energy per operation is advantageous [12], [39]. In effect, for applications where most components are often in the sleep mode, reducing the supply voltage to the minimum necessary to maintain the active circuits operational, the standby and total average power values are lower.

Digital circuits operating at  $V_{DD} = 4kT/q$  (= 103mV at 300K) were fabricated by IBM in 2001 [34]. A further reduction in the supply voltage is possible because the fundamental limit of low voltage operation for the CMOS inverter, as shown in [40], is 36mV at 300K.

In order to approximate to this limit and in an attempt to compensate for the spreading of process parameters from wafer to wafer, body bias is applied to an 1000-stage inverter chain in [41] and to a 8x8 FIR filter in [42], achieving supply voltages of only 50 mV and 85 mV, respectively. The body bias compensation technique used applies different voltages to the bodies of the PMOS and NMOS transistors. The result is a lower spread of the trip point with PVT variations. With the same purposes, in [43] a post-fabrication step is used to inject charge and correct the within-die threshold voltage variation of the MOSFETs in order to minimize the supply voltage of simple CMOS combinational logic circuits. With this technique, the supply voltage of the circuits was successfully reduced from 94 mV to 74 mV. However, the technique

requires post-fabrication steps, which can be costly in volume applications.

As part of digital systems, static random access memories (SRAM) have a particular importance in both high and low voltage applications since they dissipate as much as 70 % of the total energy as leakage energy [44], and can occupy an area of about 85 % of the die, in some applications. In [45]-[48], a non symmetric Schmitt trigger-based inverter (with no PMOS feedback mechanism) was applied to a SRAM memory (ST-SRAM) comprised of 10 transistors, in order to maximize the static noise margin and reduce power consumption. In [49] the proposed ST-SRAM was compared with other SRAM topologies with 4 to 10 transistors in the cell. The ST memory was proposed because the low supply voltage coupled with intra-die and inter-die process variations of the conventional 6-transistors SRAM and other topologies suffer from memory failures such as read failure, write failure, hold failure and access time failure. The result is that the ST-SRAM cell exhibits built-in process variation tolerance, which results in higher read, write, and hold noise margins. Moreover, as stated in [45], the 6transistor cell is *de facto* SRAM topology for both high and low voltages (actually, what makes the 6T cell the de facto topology is the number of signals to access it, three in total, and not the number of transistors). The ST-SRAM can be readily interchangeable with the 6T SRAM at higher levels of abstraction. The proposed ST-RAM retains data at a supply voltage as low as 150 mV and is able to work at a frequency of 500 Hz [48].

In [50] an energy harvesting system that accommodates both discrete-time and continuous-time energy sources was designed and validated. The system is basically formed by a pulse transformer boost converter. The startup voltage is only 36 mV, and generates an output voltage as high as  $\pm 2.5$  V. As part of the system, there is a voltage supervisor circuit, which is composed of a voltage reference, a voltage monitor, a voltage comparator made of a 6T Schmitt trigger, and an output stage. The ST is the main component of the supervisor circuit.

The same authors of [50] propose a shunt voltage regulator in [7], as part of a voltage source for energy harvesting systems intended for smart homes and environment monitoring. The system can work with one or more input sources such as photovoltaic cells, piezoelectric harvester, and thermoelectric generator. The minimum input voltage is 86 mV, and the voltage regulator is capable of sourcing  $\pm 3$  V output. The shunt voltage regulator uses a Schmitt trigger inverter as a

comparator and, due to the ST binary nature, quiescent current is essentially zero, except for the leakage current.

Lastly, in [39], a 62 mV supply voltage is applied to an 8x8-bit multiplier based on Schmitt trigger structures optimized for on-to-off current ratio maximization. The operating frequency is only 5.2 kHz, but the consumption is 17.9 nW. The NAND and NOR gates used in the multiplier were derived from the Schmitt trigger inverter aiming at the exploration of the minimum possible supply voltage for digital circuits with no post-silicon optimizations like charge injection or body biasing. The minimum supply voltage at which the circuit was fully operational was 62 mV. This remarkable result inspired the development of our research and, finally, of this thesis.

#### 1.4 SCHMITT TRIGGER ARCHITECTURES

Many Schmitt trigger architectures have been proposed along the years, in which the main active components were valves, bipolar junction transistors and MOSFETs. Valve circuits were supplied by voltages as high as 200 V, but as technology evolved and applications required lower power consumption, the supply voltages were also reduced to 12 V, 5 V, and 3.3 V. More recently, architectures and topologies intended for ultralow voltage and ultralow power applications were proposed, aiming at supply voltages in the range of 100-200 mV, or even lower. In this sense, old ST topologies or ST circuits that rely on technologies or components not proper for ultralow voltage operation such as vacuum tubes, BJTs, OP-AMPs will not be dealt with in this thesis.

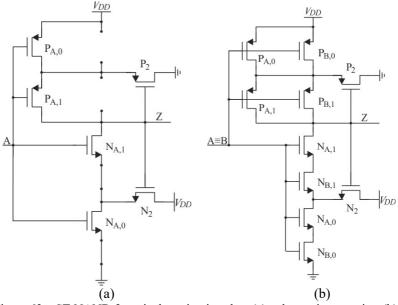

Two examples Schmitt trigger topologies are shown in Fig. 5. The one in Fig. 5 (a) was proposed in [49] whereas the one in Fig. 5 (b) was proposed in [51]. For convenience the ST circuit of Fig. 5 (a) will be explained, and is as follows: transistors  $P_1$  and  $N_1$  work as a standard inverter. However, note the parallel association of  $P_1$  and  $P_2$ , and  $N_1$  and  $N_2$ , which effectively changes the trip point of the inverter formed by  $N_1$  and  $P_1$ . For proper operation of the circuit as a Schmitt trigger,  $N_2$  and  $P_2$  must form a weak inverter if compared to the output inverter [52], formed by  $N_3$  and  $P_3$ . Actually, transistors  $N_2$  and  $P_2$  and  $N_3$  and  $P_3$  form a latch circuit, which determines the hysteretic behavior of the circuit. The analysis of the circuit of Fig. 5 (b) is similar to the one of Fig. 5 (a), considering the fact that the effective trip point of the input inverter formed by  $N_1$  and  $P_1$  depends on whether  $N_2$  is on or off.

Both the circuits in Fig. 5 (a) and (b) work as a buffer; so, in order to make these circuits invert the input signal, an additional inverter stage is required at the output, increasing area and power dissipation.

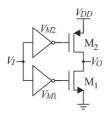

Figure 5 – Schmitt trigger buffer with parallel association of transistors: (a) latch circuit with inverters [49]; (b) NMOS network parallel association [51].

A very simple non-inverting Schmitt trigger, proposed in [53], is shown in Fig 6. The circuit is composed of two inverters with distinct transition voltages,  $V_{MI}$  and  $V_{M2}$ , and two output transistors,  $M_1$  and  $M_2$ . The hysteresis width is given by  $V_{M2}$ – $V_{MI}$ , which is effectively determined by the aspect ratios of the transistors that compose the inverters.

Figure 6 – Schmitt trigger buffer with different trip point inverters [53].

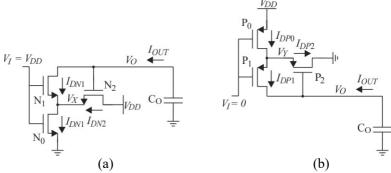

Body biasing can also be employed to change the trip point of the inverters, which form the Schmitt trigger buffers shown in Fig. 7 (a)-(b) [54].

The 4-transistor ST circuit of Fig. 7 (a) dynamically adjusts the bias voltage applied to the body of the input transistors  $N_0$  and  $P_0$ , which form an inverter. When the output voltage is low, the bias voltage applied to the body of the transistors  $N_0$  and  $P_0$  increases the trip point of the ST. On the other hand, when the output voltage is high, the trip point of the ST is decreased.

The circuit in Fig. 7 (b) is formed by three inverters, two of which are cross-coupled, forming a latch, similar to the ST from Fig. 5 (a). DTMOS transistors are employed in the first stage ( $N_0$  and  $P_0$ ) in order to vary the transconductance of the gate and to increase the speed. The second stage has two functions: first, to speed up the transition of the output voltage, and second to control the bias voltage of the third stage, since they are cross-coupled connected. The third stage ( $N_2$  and  $P_2$ ) is responsible for generating the bias voltage for the other stages. The idea of this circuit is also to vary the trip point of the topology by the application of a variable bias voltage.

Figure 7 – Schmitt trigger for ULV [54] with; (a) dynamic body-biasing; (b) cross-coupled inverters with body-biasing.

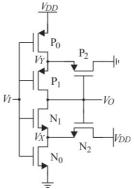

Even though some authors [53], [55] have claimed that the pile-up of four transistors between power and ground rails means that the classical CMOS Schmitt trigger, shown in Fig. 8, is not appropriate for low-voltage applications, it has been employed as the key element in several ultralow voltage (ULV) circuits as shown in Section 1.3. The classical 6T Schmitt trigger is one of the most useful circuits for both analog and digital applications [56]. Analyzing the circuit, transistors N<sub>2</sub> and P<sub>2</sub> provide voltage controlled current feedback to the middle nodes formed by transistors N<sub>0</sub>-N<sub>1</sub> and P<sub>0</sub>-P<sub>1</sub>. In this sense, the 4-transistor stacking (N<sub>0</sub>-N<sub>1</sub>-P<sub>1</sub>-P<sub>0</sub>) is of paramount importance for correct operation of the circuit since the nodes between N<sub>0</sub> and N<sub>1</sub>, and P<sub>0</sub> and P<sub>1</sub> provide a connection summing point for the feedback current. Moreover, transistor stacking has been used in [15] and [57] to reduce leakage currents effectively, while [5] claims that transistor stacking can reduce leakage current by an order of magnitude.

Figure 8 – Classical 6-transistor Schmitt trigger inverter [58].

The classical 6-transistor Schmitt trigger logic circuit, first proposed in [58], has been extensively analyzed in strong inversion in [58]-[63]. It operates roughly as follows: when the input voltage is high, both  $N_0$  and  $N_1$  are on, and the output voltage is low since there is a path between the output and the ground rail [64]. Transistor  $N_2$  is off and transistor  $P_2$  is on. However, no current flows through  $P_2$  since both  $P_0$  and  $P_1$  are off. When the input voltage is low, the transistors work in the opposite way. However, note that for a negative-going transition of the input, initially  $N_2$  is off and  $P_2$  is on, while for a positive-going transition of the input, initially  $N_2$  is on and  $P_2$  is off. Effectively, these two situations represent different strengths of the PMOS and NMOS networks, which results in two different trip points of the ST. This characterizes the hysteretic operation of the ST, when the supply voltage is high enough, as will be discussed later.

The Schmitt trigger inverter is well suited for ultralow voltage and ultralow power applications. In contrast to the bipolar and OP-AMP based ST, which have been analyzed in detail in the literature [58]-[63], little effort has been put into analyzing the ST in weak inversion, with a few in-depth studies [39],[46],[63]. In [39], the ST-based logic gates were designed for the maximization of the on-to-off current ratio, and were able to operate at a supply voltage as low as 62 mV.

One of the benefits of the ST of Fig. 8 is that, although it does not reduce leakage, it shifts the leakage path so that the output voltage is not loaded. Therefore, when the input is at 0 V and the output is high,  $N_2$  pulls  $V_X$  to a high potential. Thus, the gate-to-source voltage of  $N_1$  becomes negative biased and its drain to source voltage is close to zero.

For these two reasons, the current flowing in  $N_1$  is greatly reduced and the output voltage deviation is lower [39].

As a matter of comparison, the two ST topologies of Fig. 5 and Fig. 8 are analyzed. Although both circuits have the same number of transistors, the 4-transistors pile-up of the ST of Fig. 8, which is responsible for the feedback mechanism, provides higher voltage gain, higher noise immunity, and considerable lower dependence on process, voltage and temperature variations [65], [66]. Moreover, the ST of Fig. 5 is based on the conventional inverter, so theoretical minimum operating voltage is 36 mV. As will be detailed latter, the theoretical minimum supply voltage of the ST of Fig. 8 is 31.5 mV. Finally, the feedback mechanism present in the classical ST helps reducing the output voltage loading due to the fact that leakage current flows through transistors  $N_0$  and  $N_2$ , and  $P_0$  and  $P_2$ .

Also, note that body biasing can also be applied to the Schmitt trigger inverter and logic gates, with all benefits that the technique provides.

Other topologies of ST with discrete components, BiCMOS technology, transmission gates, variable hysteresis width control, time varying hysteresis width control, and other technologies can be found in [51], [54]-[56], and [67]-[70]. However, the main and most common topologies for ULV were presented and described here.

## 2 SCHMITT TRIGGER CONVENTIONAL OPERATION

## 2.1 WEAK INVERSION OPERATION

The behavior of the Schmitt trigger in strong inversion is well known. However, in weak inversion only partial formulations have been developed in [39]. Here, the complete analytical expressions for the Schmitt trigger operating in weak inversion are derived.

The MOSFET drain current in weak inversion is given [37], [71] by

$$I_{DN(P)} = I_{N(P)} \cdot e^{\frac{V_{GB(BG)}}{n_{N(P)} \cdot \phi_t}} \cdot \left( e^{-\frac{V_{SB(BS)}}{\phi_t}} - e^{-\frac{V_{DB(BD)}}{\phi_t}} \right)$$

(1)

$$I_{N(P)} = \mu_{N(P)} \cdot n_{N(P)} \cdot C'_{ox} \cdot \phi_t^2 \cdot \frac{W}{L} \cdot e^{-\frac{|V_{T0N(P)}|}{n_{N(P)} \cdot \phi_t} + 1}$$

(2)

where  $I_{N(P)}$  is the NMOS(PMOS) transistor strength, or current scaling factor, which is dependent on the aspect ratio W/L and the technological parameters  $\mu_{N(P)}$  (mobility),  $C'_{ox}$  (oxide capacitance per unit area), and  $V_{T0N(P)}$  (threshold voltage).  $\Phi_t = kT/q$  is the thermal voltage (25.9 mV at 300 K) and  $n_{N(P)}$  is the slope factor, usually between 1 and 2. G, S, D, and B are the gate, source, drain, and bulk nodes, respectively. For n-channel transistors, the nodal voltages referred to the bulk are positive while, for p-channel transistors, they are negative.

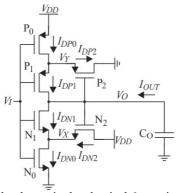

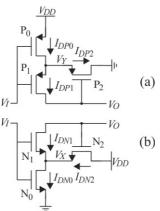

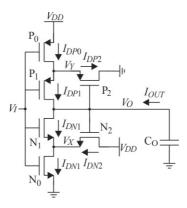

The classical 6-transistor Schmitt trigger loaded by capacitor  $C_0$  is shown in Fig. 9.

Figure 9 – Currents and voltages in the classical 6-transistor Schmitt trigger.

is

The DC equation for node  $V_X$  is:

$$I_{DN0} = I_{DN1} + I_{DN2}. (3)$$

Calculating the currents  $I_{DN0}$ ,  $I_{DN1}$ , and  $I_{DN2}$  from (1) results in

$$I_{N0} \cdot e^{\frac{V_{I}}{n_{N} \cdot \phi_{I}}} \cdot \left(1 - e^{-\frac{V_{X}}{\phi_{I}}}\right) = I_{N1} \cdot e^{\frac{V_{I}}{n_{N} \cdot \phi_{I}}} \cdot \left(e^{-\frac{V_{X}}{\phi_{I}}} - e^{-\frac{V_{O}}{\phi_{I}}}\right) + I_{N2} \cdot e^{\frac{V_{O}}{n_{N} \cdot \phi_{I}}} \cdot \left(e^{-\frac{V_{X}}{\phi_{I}}} - e^{-\frac{V_{DD}}{\phi_{I}}}\right). \tag{4}$$

Rearranging (4) for  $V_X$ , results in

$$e^{\frac{V_X}{\phi_t}} = \frac{I_{N0} + I_{N1} + I_{N2} \cdot e^{\frac{V_O - V_I}{n_N \cdot \phi_t}}}{I_{N0} + I_{N1} \cdot e^{\frac{-V_O}{\phi_t}} + I_{N2} \cdot e^{\frac{V_O - V_I}{n_N \cdot \phi_t}} \cdot e^{\frac{-V_{DD}}{\phi_t}}}.$$

(5)

Similarly, the KCL for node  $V_Y$  results in

$$e^{\frac{V_{Y}}{\phi_{i}}} = \frac{I_{P0} \cdot e^{\frac{V_{DD}}{\phi_{i}}} + I_{P1} \cdot e^{\frac{V_{O}}{\phi_{i}}} + I_{P2} \cdot e^{\frac{V_{I} - V_{O}}{n_{P} \cdot \phi_{i}}}}{\frac{V_{I} - V_{O}}{I_{P0}} + I_{P1} + I_{P2} \cdot e^{\frac{V_{I} - V_{O}}{n_{P} \cdot \phi_{i}}}}$$

(6)

At the same time, the KCL for the unloaded node  $V_O$ ,  $(I_{OUT} = 0)$ ,

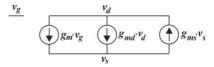

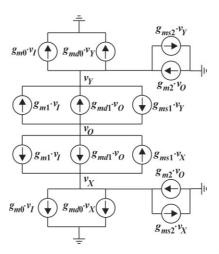

$$I_{DN1} = I_{DP1}. (7)$$