# DESIGN TRADEOFFS OF CMOS CURRENT MIRRORS USING ONE-EQUATION FOR ALL-REGION MODEL

Ahmed Emira<sup>1</sup>, Edgar Sánchez-Sinencio<sup>1</sup>, and Márcio Schneider<sup>2</sup>

<sup>1</sup>Analog & Mixed Signal Center, Electrical Engineering Dept., Texas A&M University, College Station, Texas 77843

<sup>2</sup>Universidade Federal de Santa Catarina, Florianópolis, SC 88040-900 Brazil

## **ABSTRACT**

The design of current mirror involves different conflicting design specifications (noise, bandwidth, input and output resistances, power dissipation, accuracy, THD, etc..), while only three design transistor parameters are available (DC current, width, length). In this paper, we address the effect of such parameters on the current mirror performance. For each specification, an expression is derived which is valid for any inversion level based on the one-equation for all-region MOS model [1]. Experimental results from a current mirror fabricated in 0.5µm AMI CMOS process are found in good agreement with the theoretical ones.

#### 1. INTRODUCTION

Current mirrors have been taking part in almost all analog integrated circuits. In most cases, the performance of these circuits is limited by the non-idealities of the current mirror. In this paper, the one-equation model derived in [1] for MOS transistor is used to analyze the performance of the simple current mirror shown in Fig. 1, where  $A_I$  is the required current gain, W/L and  $A_I$ W/L are the aspect ratios of the input and output transistors, respectively. The output transistor  $M_2$  is assumed to operate in saturation. The model equations for the saturation region are listed below for convenience.

$$V_{p} = \left[ \sqrt{V_{G} - V_{T0} + (\sqrt{\phi_{0}} + \gamma/2)^{2}} - \gamma/2 \right]^{2} - \phi_{0}$$

$$\approx \frac{V_{G} - V_{T0}}{n}$$

(1)

where:

$$n = 1 + \frac{\gamma}{2\sqrt{\phi_o + V_n}} \qquad \phi_o = 2\phi_F \tag{2}$$

$$I_{s} = 0.5 n\mu C_{ox} \varphi_{i}^{2} \frac{W}{L} = normalization current$$

(3)

$$i_{f} = \frac{I}{I_{S}} = \frac{I(V_{G}, V_{S})}{I_{S}}$$

$$V_{dd}$$

$$I_{in}$$

$$M_{1}$$

$$M_{2}$$

$$M_{2}$$

$$M_{2}$$

Fig. 1 Simple current mirror

$$\frac{V_p - V_{S(D)}}{\varphi_t} = \sqrt{1 + i_f} - 2 + \ln(\sqrt{1 + i_f} - 1)$$

(5)

where

V<sub>p</sub> is the pinch-off voltage [1].

V<sub>T0</sub> is the threshold voltage in equilibrium.

γ is the body effect factor.

$\phi_F$  is the Fermi potential for holes.

$i_f$  is the forward current inversion level.

I is the drain current.

$\mu$  is the low field mobility.

$C_{ox}$  is the gate oxide capacitance/unit area.

$\phi_t$  is the thermal voltage.

n is the sub-threshold slope factor [1], slightly dependent on  $V_G$ , greater than one and usually less than two. In this paper, n = 4/3 is used to simplify the analyses.

# 2. ANALYSIS OF THE CURRENT MIRROR

In each of the following subsections, simulation results using version 3.1 BSIM models will be compared with the theoretical results. Measurement results, from a current mirror fabricated in 0.5 $\mu$ m CMOS process, will also be presented. Unless otherwise stated, all simulations and measurements are done with W = 120 $\mu$ m, L =1.2 $\mu$ m, and A<sub>1</sub> = 1. Note that, since V<sub>GS1</sub> = V<sub>GS2</sub>, M1 and M2 will have the same inversion level ( $i_f$ ).

# 2.1. Output and input resistances

In the saturation region, channel length modulation and drain-induced barrier lowering (DIBL) are the main factors limiting the output resistance of an MOS transistor. To take into account these two effects, the following empirical formula can be used:

$$R_{out} = \frac{LV_A}{A_I I_{Sl} i_f^{\alpha}} \tag{6}$$

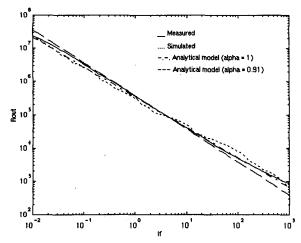

where  $V_A$  is the Early voltage / unit length,  $I_{S1}$  is the normalization current of the input transistor, and  $\alpha$  is a parameter usually assumed to be equal to one. However, in order to have a better fit of equations (6) with the measurement results,  $\alpha$  is chosen slightly smaller than one. (about 0.9 in 0.5 $\mu$ m AMI CMOS technology). Fig. 2 shows the simulated and measured output resistance together with the expected output resistance for  $\alpha = 1$  and  $\alpha = 0.91$ . It was found that the maximum deviation error in the expected  $R_{out}$  is 18% for  $\alpha = 0.91$  and 50% for  $\alpha = 1$ .

The input resistance of the simple current mirror is given by:

$$R_{in} = \frac{\partial V_{in}}{\partial I_{in}} = \frac{\partial V_{GS}}{I_{S1} \partial i_f} = \frac{n \varphi_t}{2I_{S1}} \left( \frac{1}{\sqrt{1 + i_f} - 1} \right)$$

(7)

Fig. 2 Output resistance of the current mirror

## 2.2. Current gain errors

Accuracy of the current mirror is mainly limited by three parameters, namely,  $V_{T0}$  mismatch,  $\beta$  mismatch, and the finite output resistance of the transistor. The current gain error (CGE) due to  $V_{T0}$  mismatch can be derived from (5):

error (CGE) due to

$$V_{T0}$$

mismatch can be derived from (5):

$$CGE|_{V_{T}} = \frac{\Delta I}{I} = -2 \frac{\sqrt{1 + i_{f}} - 1}{i_{f}} \frac{\Delta V_{T0}}{n \varphi_{t}} = \begin{cases} -\frac{\Delta V_{T0}}{n \varphi_{t}} & i_{f} >> 1 \\ -\frac{2}{\sqrt{i_{f}}} \frac{\Delta V_{T0}}{n \varphi_{t}} & i_{f} >> 1 \end{cases}$$

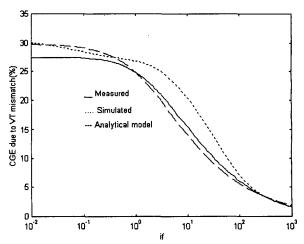

(8)

where  $\Delta V_{T0} = V_{T2} - V_{T1}$  and  $\Delta I = I_2 - I_1$ . The above equation shows that the CGE due to V<sub>T0</sub> mismatch increases when if is decreased. However, this error becomes less dependent on if in the weak inversion region  $(i_f < 1)$ . Note the equation reduces to the well-known CGE at the weak and strong inversion regions. The CGE is independent of  $i_f$  in the weak inversion region because of the exponential IV characteristic. The simulated and theoretical errors of a current mirror in 0.5µm technology are shown in Fig. 3, for  $\Delta V_{T0}$ = -10mV. Since it is not possible to control the V<sub>T0</sub> mismatch between the transistors M1 and M2, the mismatch is artificially imposed by offsetting the gate voltage of M2 by 10mV with respect to that of M1. A well-matched current mirror  $(\Delta V_{T0} < 1 \text{mV})$  is chosen for this measurement to ensure that the total effective mismatch is close to 10mV. The theoretical and simulated CGEs match well in the strong and weak inversion regions. However, the difference reaches its maximum value (about 40%) at  $i_f = 1$ . In the same figure, the measured CGE is shown to be well matched with the theoretical curve in the whole inversion regime with maximum error of only 10%. This shows the superior accuracy of the all-region model over BSIM model. The figure also shows that the sensitivity to V<sub>T0</sub> mismatch increases at weak inversion.

Fig. 3 The CGE due to V<sub>T0</sub> mismatch

The second factor that determines the accuracy of the current mirror is the mismatch in the transconductance parameter ( $\beta$ ). Since the output current of the transistor is linearly proportional to  $\beta$ , then:

$$CGE\big|_{\beta \text{ mismatch}} = \frac{\Delta\beta}{\beta} \tag{9}$$

where  $\beta$  is defined as:

$$\beta = \mu C_{ox} \frac{W}{L} \tag{10}$$

Note that, as expected,  $\beta$  mismatch leads to a CGE that is independent of the inversion level ( $i_f$ ).

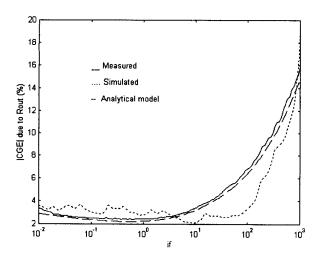

The third factor that affects the CGE is the output resistance of the transistor. The CGE due to output resistance depends on the load resistance of the current mirror. It's a common practice to evaluate this type of error when the current mirror is loaded with a similar current mirror. In other words, we will calculate the CGE due to output resistance when the load resistance is the same as the input resistance of the current mirror. In this case, the CGE is expressed as:

$$CGE\big|_{Rout} = -\frac{R_{in2}}{R_{out}} = -\frac{n\varphi_t}{2LV_A} \left(\frac{i_f^{\alpha}}{\sqrt{1 + i_f} - 1}\right)$$

(11)

where  $R_{in2}$  is the input resistance of the next stage, which is assumed to be a current mirror with the same aspect ratio as M2 and the same inversion level. This is illustrated in Fig. 4, in which it is shown that the CGE magnitude exhibits a minimum of about 2.5% at  $i_f = 0.072$  in the theoretical model, which is close enough to the measured minimum value 2.44% at  $i_f = 0.05$ . The CGE starts to increase in the moderate and strong inversion regions. Note also that, from (11), the CGE can be reduced by increasing the length of the transistor. Unfortunately, this will reduce the bandwidth and increase the area of the current mirror.

Fig. 4 The CGE due to output resistance

#### 2.3. Noise

The input referred thermal noise current can be expressed as:

$$\overline{i_{ni}^2} = \overline{i_{n1}^2} + \frac{1}{A_I^2} \overline{i_{n2}^2} \tag{12}$$

From [2], for an MOS transistor, the input referred noise is given by:

$$\overline{i_n^2} = -4kT \frac{\mu}{L^2} Q_I \Delta f \tag{13}$$

where  $Q_I$  is the total inversion layer charge. It can be calculated by integrating the inversion charge density over the transistor area:

$$Q_I = W \int_0^L Q_I(x) dx \tag{14}$$

From [1]:

$$I_D = \mu W \left( \frac{-Q_I(x)}{nC_{ox}} + \varphi_t \right) \frac{dQ_I(x)}{dx}$$

(15)

From equations (14) and (15):

$$Q_{I} = \frac{\mu W}{I_{D}} \left( \frac{-(Q_{ID}^{'3} - Q_{IS}^{'3})}{3nC_{ox}} + \varphi_{I} \frac{Q_{ID}^{'2} - Q_{IS}^{'2}}{2} \right)$$

(16)

where Q'<sub>ID</sub> and Q'<sub>IS</sub> are the inversion charge densities at the drain and source, respectively, and can be expressed in terms of the inversion level as follows [1]:

$$Q_{IS(D)}' = -nC_{ox}\varphi_t \left( \sqrt{1 + i_{f(r)}} - 1 \right)$$

(17)

Substituting in (16) and noting that the reverse inversion level  $(i_r)$  is zero for a saturated transistor, then:

$$Q_{I} = \frac{\mu W \varphi_{I} (n C_{ox} \varphi_{I})^{2}}{I} \left( \frac{1}{3} (1 + i_{f})^{\frac{3}{2}} - \frac{1}{2} (1 + i_{f}) + \frac{1}{6} \right)$$

(18)

Using (3), (4), (12), (13), and (18), we obtain:

$$\overline{i_{ni}^2} = 16 q I_{S1} \left( 1 + \frac{1}{A_I} \right) \left( \frac{\frac{1}{3} (1 + i_f)^{\frac{3}{2}} - \frac{1}{2} (1 + i_f) + \frac{1}{6}}{i_f} \right) \Delta f$$

(19)

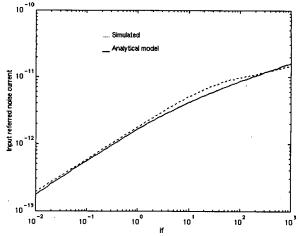

Fig. 5 The input referred noise current

Fig. 5 shows the theoretical and simulated input referred noise current densities in  $A/\sqrt{Hz}$  for unity current gain. The two curves are fairly close to each other in the weak and strong inversion regions. In moderate inversion, the simulated curve deviates from the theoretical equation (19). The deviation error is less than 20%, which may be acceptable for noise calculations.

#### 2.4. The bandwidth

The bandwidth of the current mirror is often dominated by the input time constant, which can be expressed as:

$$BW = \frac{g_{in}}{2\pi C_{in}} = \frac{g_{m1}}{2\pi (C_{gb1} + C_{gb2} + C_{gs1} + C_{gs2})}$$

(20)

which can roughly be approximated as:

$$BW \cong \frac{\mu n \varphi_t}{(1+A_t)\pi L^2} \left( \sqrt{1+i_f} - 1 \right) \tag{21}$$

The bandwidth is directly proportional to the transconductance  $g_m$  since the sum of the capacitances in the denominator of (20) is almost independent of  $i_f$ . Indeed, the denominator of (20) can be written as approximately  $C_{ox}WL/2(1+A_I)$  and (21) results as a consequence of this approximation. Although this expression does not take into account the effect of drain and source overlap capacitances, these capacitances can be easily added to the denominator of (20). Neglecting this effect has led to a slight error in the theoretical bandwidth.

# 2.5. Input and Output Voltages

The minimum power supply is limited by the required input gate to source voltage. This voltage can be directly derived from (5):

$$V_{\text{lm}in} = V_T + n\varphi_i \left( \sqrt{1 + i_f} - 2 + \ln(\sqrt{1 + i_f} - 1) \right)$$

(22)

For the weak inversion region  $(i_f < 1)$ , the current mirror can operate properly from a supply voltage as low as 1V while having sufficient room for the signal swing. Accordingly, the weak inversion region is more appropriate for very low voltage applications. However, the bandwidth is reduced as  $i_f$  decreases. This limits the use of this region to low frequency applications. In contrast, for the strong inversion region, the input voltage increases rapidly with  $i_f$ . The corresponding increase in the bandwidth is not as much. For most applications, with modest bandwidth and power supply specifications, the moderate inversion region may be sufficient.

# 2.5. The total harmonic distortion (THD)

The total harmonic distortion of the current mirror is dominated by  $V_{T0}$  mismatch. We assume that the total input current is given by:

$$I_1 = I_{bias} + \Delta I_1 \tag{23}$$

where  $I_{bias}$  is the bias current and  $\Delta I_1$  is the signal current. From Taylor series expansion around  $\Delta V_{T0} = 0$ , the inversion level in the output transistor M2 is given by:

$$i_{f2} \cong i_{f1} - \frac{2}{n\varphi_t} \left( \sqrt{1 + i_{f1}} - 1 \right) \Delta V_T$$

(24)

where  $\Delta V_T = V_{T2} - V_{T1}$ .

Now, if  $I_1$  is a sinusoidal current with amplitude  $\Delta I_{1m}$ , then the second and third order harmonics in the output current can be calculated. Let  $i_{fl} = i_{fbias} + \Delta i_{fl}$ , then by expanding (24) around  $\Delta i_{fl} = 0$ , it can be shown that the second and third order harmonics due to  $V_{T0}$  mismatch are approximated by:

$$HD_2 = \frac{\Delta V_T}{8n\varphi_i} \frac{i_{f1}}{\left(1 + i_{f1}\right)^{\frac{3}{2}}} \frac{\Delta I_{1m}}{I_{S1}i_{f1}}$$

(25)

$$HD_{3} = \frac{\Delta V_{T}}{32n\varphi_{i}} \frac{i_{f1}^{2}}{\left(1 + i_{f1}\right)^{5}} \left(\frac{\Delta I_{1m}}{I_{S1}i_{f1}}\right)^{2}$$

(26)

#### 3. CONCLUSION

The basic CMOS current mirror has been analyzed using the all-region model. Expressions for design specifications of current mirrors as function of the inversion level were provided. Measurement results showed the model accuracy despite its relative simplicity. At least in the CGE prediction, the all-region model gives better accuracy than the more complicated BSIM models.

## 4. ACKNOWLEDGEMENT

The authors would like to thank Motorola for the partial financial support.

### 5. REFERENCES

[1] A. I. A. Cunha, M. C. Schneider, C. Galup-Montoro, "An MOS Transistor Model for Analog Circuit Design," IEEE JSSC, vol. 33, no. 10, pp. 1510-1519, Oct. 1998.

[2] S. Tedja, J. V. Spiegel, H. H. Williams, "Analytical and Experimental Studies of Thermal Noise in MOSFET's," IEEE Trans. Electron Devices, vol. 41, no. 11, Nov. 1994.