# Charge-Based Definition of Threshold Voltage for Undoped Body MOSFETs

A. I. A. Cunha\*\*, C. Galup-Montoro\* and M. C. Schneider\*

\*Department of Electrical Engineering, Federal University of Santa Catarina, Campus Universitario, Trindade, CEP 88040-900, Florianopolis, Brazil, marcio@eel.ufsc.br, carlos@eel.ufsc.br

\*\*Department of Electrical Engineering, Federal University of Bahia, Escola Politecnica, Rua Aristides Novis 2, CEP 40210-630, Salvador, Brazil, aiac@ufba.br

## **ABSTRACT**

This paper presents a charge-based definition of the threshold voltage for both intrinsic single gate and dual gate MOSFETs. An unambiguous physical condition is used in order to determine the mobile charge density at threshold. The corresponding surface potential is determined from the solution of Poisson-Boltzmann equation in the silicon film. The threshold voltage evaluated from the charge-based definition is compared with threshold voltages determined from other definitions.

Keywords: threshold voltage, intrinsic MOSFET, DG-MOSFET

## 1 INTRODUCTION

Double-gate (DG) MOSFETs with undoped body have been proposed for nanometer size CMOS [1-4]. DG minimizes short-channel effects and the absence of impurity atoms in the channel avoids fluctuations in the characteristics of very small devices. There is no consensus in the technical community about threshold voltage definition of intrinsic channel devices, in spite of their increasing importance [4]. Clearly, the conventional definition as the gate voltage for which the minority carrier concentration at the semiconductor interface equals the majority carrier concentration in the bulk is meaningless for intrinsic substrates.

Several criteria have been proposed to derive or extend threshold voltage definitions to undoped MOSFETs [4], most of them failing to provide simultaneously a physical meaning, unambiguity in the extraction methodology and a proper description of the dependence upon silicon and insulator thicknesses in DG devices.

In this paper we show that a charge-based definition of threshold, already applied to conventional bulk MOSFETs [5, 6], is well suited to the undoped single gate and symmetric double gate MOSFETs. Owing to its simplicity, we analyze first the hypothetical case of a single gate MOSFET on an intrinsic substrate. Next, the DG MOSFET is modeled and simulation results that compare different definitions of the threshold voltage are provided.

## 2 FUNDAMENTALS

Neglecting the hole charge for an undoped or lightly doped body n-channel MOSFET, the voltage balance equation [1] is

$$Q'_{e} = -C'_{ox} (V_{G} - V_{FB} - \phi_{S})$$

(1)

where  $Q'_e$  is the electron charge density for single-gate devices and half the mobile charge density for double-gate devices,  $V_G$  is the gate voltage,  $V_{FB}$  is the flat-band voltage, and  $\phi_S$  is the surface potential,  $C'_{ox} = \varepsilon_{ox}/t_{ox}$  is the oxide capacitance per unit area,  $\varepsilon_{ox}$  is the oxide electrical permittivity and  $t_{ox}$  is the gate oxide thickness.

# 2.1 Intrinsic single-gate MOSFETs

Solving Poisson-Boltzmann equation for the n-channel intrinsic single-gate MOSFET, neglecting holes, we obtain [1]:

$$Q_e' = -\sqrt{2q\varepsilon_{Si}n_i\phi_i}e^{(\phi_s - V_C)/(2\phi_i)}$$

(2)

where q is the elementary charge,  $n_i$  is the intrinsic concentration,  $\varepsilon_{Si}$  is the electrical permittivity of silicon,  $V_C$  is the channel voltage (quasi-Fermi level of electrons) and  $\phi_i$  is the thermal voltage. The single gate intrinsic bulk MOSFET is not a much useful device because of the low value of the subthreshold slope of the charge (current) characteristic, around 120 mV/dec at room temperature. Combining (1) and (2) the surface potential is determined for given values of  $V_G$  and  $V_C$ .

# 2.2 Intrinsic symmetric double-gate MOSFETs

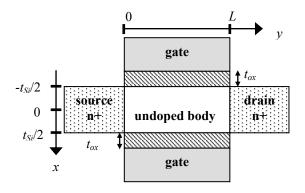

The solution of the Poisson-Boltzmann equation in the case of an N-channel intrinsic symmetric dual gate MOSFET (Fig.1) leads to [3]:

$$\phi(x,y) = V_C(y) - 2\phi_t \ln \left[ \frac{t_{Si}}{4\beta L_{Di}} \cos\left(2\beta \frac{x}{t_{Si}}\right) \right]$$

(3.a)

$$\phi_{S}(y) = V_{C}(y) - 2\phi_{t} \ln \left[ \frac{t_{Si}}{4\beta L_{Di}} \cos(\beta) \right]$$

(3.b)

$$Q_{e}' = -4C_{si}\phi_{t}\beta \tan\beta \tag{3.c}$$

$$\frac{V_G - V_{FB} - V_C}{2\phi_t} - ln\left(\frac{4L_{Di}}{t_{Si}}\right) = ln\left(\frac{\beta}{\cos\beta}\right) + 2\frac{C'_{Si}}{C'_{ox}}\beta\tan\beta \quad (3.d)$$

where  $\phi_S(y) = \phi(x,y)$  for  $x = \pm t_{Si}/2$ , and  $t_{Si}$  is the silicon film thickness. The other parameters in expressions (3) are the silicon-film capacitance per unit area and the intrinsic Debye length, given respectively by  $C'_{Si} = \varepsilon_{Si}/t_{Si}$  and  $L_{Di} = \sqrt{\varepsilon_{Si}\phi_i/(2qn_i)}$ .

$L_{Di}$  is of the order of 100  $\mu$ m at room temperature. The auxiliary variable  $\beta$  is directly associated with the carrier charge density, as (3.c) shows.

Figure 1: Schematic diagram of an N-channel intrinsic symmetric DG MOSFET

# 3 THRESHOLD VOLTAGE DEFINITION

The charge-based definition of threshold in MOS transistors is based on a physically meaningful value for the charge carrier density at threshold, namely the thermal charge density, which is defined as the effective channel capacitance per unit area times the thermal voltage [7, 8]. For conventional planar transistors, the effective capacitance is  $nC'_{ox}$ , where n depends on the substrate doping, typical values lying in the interval 1.2-1.5. When the channel charge density equals the thermal charge density, the drift and diffusion components of the channel current are equal [7, 8]. Below threshold the transport is dominated by diffusion, above threshold the prevailing transport mechanism is drift. Thus, the thermal charge corresponds to the transition between a region where

transport is dominated by diffusion to another one, where drift prevails. A useful procedure to determine directly the charge-based threshold condition is to determine the bias point of the transistor in the linear region where the transconductance-to-current ratio drops to one-half of its peak value [5, 6].

In the following we will show that the above properties continue valid for intrinsic body MOSFETs.

According to a charge-based approach, the threshold voltage in equilibrium  $V_{T0}$  for undoped body devices is defined as the gate voltage  $V_G$  corresponding to the threshold mobile charge density. From (1), with  $V_C = 0$ :

$$V_{T0} = V_{FB} + \phi_{ST} - Q'_{eT} / C'_{ox}$$

(4)

where  $\phi_{sT}$  and  $Q'_{eT}$  are the surface potential and the mobile charge density at threshold.

# 3.1 Intrinsic single gate MOSFETs

For an undoped body planar MOSFET, n = 1, and the threshold charge, which is assumed equal to the thermal charge, is given by

$$Q'_{eT} = -C'_{ox}\phi_t \tag{5}$$

Substituting (5) into (2), with  $Q'_e = Q'_{eT}$ , and solving for  $\phi_s$  with  $V_C = 0$ , we find:

$$\phi_{ST} = \phi_t \ln \left( \frac{\phi_t}{2qn_t \varepsilon_{Si}} \frac{\varepsilon_{ox}^2}{t_{ox}^2} \right) = 2\phi_t \ln \left( \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{L_{Di}}{t_{ox}} \right)$$

(6)

Substituting (5) and (6) into (4) yields

$$V_{T0} = V_{FB} + \phi_t \left[ 2 \ln \left( \frac{\varepsilon_{ox}}{\varepsilon_{Si}} \frac{L_{Di}}{t_{ox}} \right) + 1 \right]$$

(7)

Equation (7) gives exactly the same value for the threshold voltage as that obtained from the second derivative method [4].

# 3.2 Intrinsic symmetric dual gate MOSFETs

According to the  $g_m/I_D$  extraction methodology, the threshold voltage in equilibrium is the value of  $V_G$ , in the linear region, for which  $g_m/I_D$  drops to one half of its maximum value (in subthreshold). For low values (typically less than 10 mV) of drain-to-source voltage ( $V_{DS}$ ):

$$(\partial Q_e'/\partial V_G)/Q_e' \cong g_m/I_D \tag{8}$$

Therefore, a condition for determining the mobile charge density arouses from this criterion.

Differentiating (3.c) with respect to  $V_G$  gives:

$$\frac{\partial Q_e'}{\partial V_G} = -4C_{Si}'\phi_t \left(\tan\beta + \beta + \beta \tan^2\beta\right) \frac{\partial\beta}{\partial V_G}$$

(9)

From (3.d) (for  $V_C = 0$ ) we can find the derivative in the right-hand side of (9), which allows us to write

$$\frac{\partial Q'_{e}}{\partial V_{G}} \frac{1}{Q'_{e}} = \frac{\left(\tan \beta + \beta + \beta \tan^{2} \beta\right) / \left(2\phi_{t} \tan \beta\right)}{\left[1 + \beta \tan \beta + \frac{2C'_{Si}}{C'_{ox}} \left(\beta \tan \beta + \beta^{2} \tan^{2} \beta + \beta^{2}\right)\right]}$$

(10)

Since the maximum value of the expression in the right-hand side of (10) is  $I/\phi_t$ , the value of  $\beta$ , according to the  $g_m/I_D$  extraction methodology, is the solution ( $\beta_T$ ) of:

$$\tan \beta_T \left( \tan \beta_T + \beta_T + \beta_T \tan^2 \beta_T \right) = \frac{C'_{ox}}{2C'_{Si}}$$

(11)

Therefore, the threshold voltage is given by (4) where  $Q'_{eT}$  and  $\phi_{ST}$  are calculated from (3.c) and (3.b), respectively, with  $\beta = \beta_T$ , evaluated according to (11).

As shown in the Appendix, Eq. (10) also gives the condition of equality between the drift and diffusion components of the channel current for low values of  $V_{DS}$ . Thus, the physical meaning of the extracted threshold is exactly the same as in the case of conventional planar transistors.

# 4 SIMULATION RESULTS

Some simulations concerning the threshold voltage of the intrinsic symmetric dual gate MOSFET are now presented. Several different ratios between silicon and oxide thicknesses have been considered, from  $t_{Si}/t_{ox} = 0.3$  ( $C'_{ox}/C'_{Si} = 0.1$ ) to  $t_{Si}/t_{ox} = 30$  ( $C'_{ox}/C'_{Si} = 10$ ).

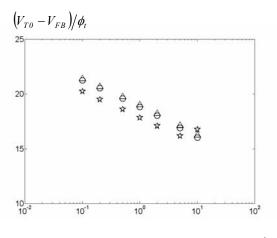

Fig. 2 compares the threshold voltage calculated using expression (4) (with  $\phi_{ST}$  and  $Q'_{eT}$  calculated from (3.b) and (3.c), respectively using the value of  $\beta_T$  determined with (11)) with the threshold voltage determined from two extraction methodologies applied to theoretical current characteristics [3]: the maximum of second derivative method [4] and the  $g_m/I_D$  method [5, 6]. As expected, the definition of the threshold voltage  $V_{T0}$  proposed here and the  $g_m/I_D$  extraction methodology exhibit very good matching. On the other hand, the threshold voltage determined by the extreme of the second derivative displays a deviation with respect to the other two methods which does not exceed one thermal voltage.

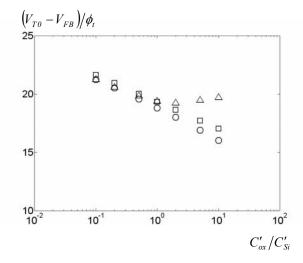

In Fig.3,  $V_{T0}$  calculated, once again using the value of  $\beta_T$  determined with (11), is compared with two other definitions: the vanishing of extrapolated supra-threshold mobile charge density [4, 9] (charge-based) and the crossover between surface potential behaviors [4]

(phenomenological). According to the later, threshold voltage is the value of  $V_G$  for which the derivatives of  $\phi_S$  and  $-Q_e'/C'_{ox}$  with respect to  $V_G$  are equal one to each other, and thus to 1/2 [4]. The three definitions agree very well except for thick silicon films where the phenomenological definition of [4] proves to be less sensitive to the ratio between oxide and silicon capacitances.

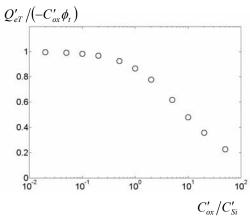

Fig.4 shows the mobile charge density for which drift equals diffusion versus the ratio  $C'_{ox}/C'_{Si}$ . It can be noticed that half the carrier charge density inside the silicon film at threshold approaches the thermal charge for very thin silicon films. This limit is easily determined from (11) applying the limit when  $\beta_T$  approaches zero.

$C'_{ox}/C'_{Si}$

Figure 2: Threshold voltage of intrinsic symmetric DG MOSFET, calculated from condition (11) (circles) and extracted from:  $g_m/I_D$  methodology (triangles); maximum of second derivative method (stars).  $t_{ox}$ = 2 nm.

Figure 3: Threshold voltage of intrinsic symmetric DG MOSFET, calculated from: condition (11) (circles); charge-based criterion of [9] (squares) and phenomenological definition of [4] (triangles).  $t_{ox} = 2$  nm.

Figure 4: Half threshold mobile charge of intrinsic symmetric dual gate MOSFET.  $t_{ox} = 2$  nm.

# 5 CONCLUSIONS

Charge-based definitions of threshold for conventional bulk MOS transistors have been extended to undoped body devices.

In the case of intrinsic symmetric DG MOSFETs, theoretical analysis and simulation results show that the proposed definition, based on the relative variation of the carrier charge density with the gate voltage, conciliates a phenomenological criterion ( $I_{Ddrit} = I_{Ddiff}$ ) and a simple extraction methodology ( $g_m/I_D$ ).

## AKNOWLEDGMENTS

The authors would like to thank CAPES and CNPq for the financial support.

## APPENDIX

According to the Pao-Sah model, the drain current in a DG MOSFET is:

$$I_D = I_{Ddrift} + I_{Ddiff} = -2 \mu W Q'_e dV_C / dy$$

(A1)

where  $\mu$  is the electron mobility, assumed to be constant, and W is the channel width. The diffusion component of the current is

$$I_{Ddiff} = 2\mu W \phi_t \, dQ_e' / dy \tag{A2}$$

Using (A1) and (A2), the condition  $I_{Ddrift} = I_{Ddiff}$  is fulfilled if

$$-\mu W Q'_e \frac{dV_C}{dv} = 2\mu W \phi_t \frac{dQ'_e}{dv} \rightarrow \frac{\partial Q'_e}{\partial V_C} \frac{1}{Q'_e} = -\frac{1}{2\phi_e}$$

(A3)

From expression (3.d), one can readily conclude that the dependence of the charge density (or, equivalently,  $\beta$ ) on  $V_C$  is, apart from the negative sign, the same as the

dependence on  $V_G$ . Therefore, we conclude that condition (A3) is equivalent to the condition

$$\left(\partial Q_{e}^{\prime}/\partial V_{G}\right)/Q_{e}^{\prime} = I/(2\phi_{t}) \tag{A4}$$

which has been used to derive the value of the charge density to calculate the threshold voltage. Therefore, the condition  $I_{Ddrift}=I_{Ddiff}$  to define the threshold is equivalent to (A4) and, consequently, to the  $g_m/I_D$  method to extract the threshold voltage.

# **REFERENCES**

- [1] A. Ortiz-Conde, F.J. García Sánchez, M. Guzmán, "Exact analytical solution of channel surface potential as an explicit function of gate voltage in undopedbody MOSFETs using the Lambert W function and a threshold voltage definition there from," *Solid-State Electronics*, 2003, pp. 2067-2073.

- [2] Y. Taur, "Analytic solutions of charge and capacitance in symmetric and asymmetric double-gate MOSFETs," *IEEE Transactions on Electron Devices*, vol. 48, no.12, 2001, pp. 2861-2869.

- [3] Y. Taur, X. Liang, W. Wang, H. Lu, "A continuous, analytic drain-current model for DG MOSFETs," *IEEE Electron Device Letters*, vol. 25, no.2, 2004, pp. 107-109.

- [4] F.J. García Sánchez, A. Ortiz-Conde, J. Muci, "Understanding threshold voltage in undoped-body MOSFETs: An appraisal of various criteria," *Microelectronics Reliability*, 2006, pp. 731-742.

- [5] A.I.A. Cunha, M.C. Schneider, C. Galup-Montoro, C.D.C. Caetano and M.B. Machado, "Unambiguous extraction of threshold voltage based on the ACM model," in Proceedings of Nanotech 2005, Workshop on Compact Modeling (WCM), Anaheim, CA, May 2005, pp. 139-142

- [6] M.C. Schneider, C. Galup-Montoro, M.B. Machado and A.I.A. Cunha, "Interrelations between threshold voltage definitions and extraction methods," in Proceedings of Nanotech 2006, Workshop on Compact Modeling (WCM), Boston, MA, May 2006, pp. 868-871.

- [7] C. Galup-Montoro, M.C. Schneider, and A.I.A. Cunha, "A current-based MOSFET model for integrated circuit design," In: Sánchez-Sinencio, Andreou A. editors. Low-Voltage/Low-Power Integrated Circuits and Systems, IEEE Press, 1999, pp. 7-55.

- [8] C. Galup-Montoro and M.C. Schneider, MOSFET Modeling for Circuit Analysis and Design, World Scientific, Singapore, 2007.

- [9] J.-M. Sallese, F. Krummenacher, F. Pregaldiny, C. Lallement, A. Roy, and C. Enz, "A design oriented charge-based current model with the EKV formalism," *Solid-State Electronics*, 2005, pp. 485-489.