# **Extraction of Mosfet Effective Channel Length and Width Based on the Transconductance-to-Current Ratio**

A. I. A. Cunha\*, M. C. Schneider, C. Galup-Montoro, C. D. C. Caetano, and M. B. Machado

Department of Electrical Engineering, Federal University of Santa Catarina, Florianópolis, SC, CEP 88040-900, Brazil,

\*Department of Electrical Engineering, Federal University of Bahia

Escola Politécnica, Salvador, BA, CEP 40210-630, Brazil

E-mails: aiac@ufba.br, {marcio, carlos, cleber, marciobm}@eel.ufsc.br

## **ABSTRACT**

This paper presents a very simple methodology for determining the effective channel length and width, which is independent of the determination of the threshold voltage. The procedure is based on measurement of the transconductance-to-current ratio  $(g_m/I_D)$  characteristic of the MOSFET in the linear region, from weak to moderate inversion. For the extraction of both the effective channel length and width, the  $g_m/I_D$  characteristic is determined for several devices of different mask channel lengths and widths, respectively. The methodology of extraction has been applied to devices of 0.35 and 0.18 $\mu$ m CMOS technologies.

**Keywords**: extraction, effective channel length, transconductance-to-current ratio

## 1 INTRODUCTION

The MOSFET effective channel length is a very useful parameter for circuit design and simulation as well as for technology characterization. Although related to the metallurgical length, shorter than the mask length owing to lateral diffusion, the effective channel length is rather an electrical parameter [1], [2] to which drain current is inversely proportional. Its determination is strongly correlated with the measurement and modeling of the I-V characteristics and is frequently associated with the extraction of threshold voltage [1], [2].

So far, the most apparent difficulties in the extraction of effective channel length are (i) its dependence upon an accurate determination of threshold voltage, (ii) influence of extrinsic resistances, and (iii) complexity introduced by the algorithm usually employed to extract it. Most available methodologies suffer from at least one of these problems, for instance, the channel resistance method [1] and  $V_{\rm GS}$ -method [3] suffer from (i) and (ii) while the shift and ratio method [1] suffers from (iii).

The methodology proposed here for extracting both the effective channel length and width is based on the determination of the specific current, which is a model parameter that incorporates the contributions of both channel length and width to the drain current. The procedure for extracting the effective channel length and width is extremely simple, reliable, and independent of the determination of such parameters as the threshold voltage or series resistances.

### 2 THE ACM MODEL

The ACM (Advanced Compact MOSFET) model consists of simple, accurate, and single equations that represent the device behavior in all regimes of operation, using well-known physical parameters [4], [5]. According to the ACM model

$$I_{D} = I_{S} (i_{f} - i_{r}) \tag{1}$$

$$I_{S} = \mu C_{ox}' n \frac{\phi_{t}^{2}}{2} \frac{W}{L}$$

(2)

$$\frac{g_m}{I_D} \cong \frac{2}{n\phi_t \left(\sqrt{1+i_f} + \sqrt{1+i_r}\right)} = \left(\frac{g_m}{I_D}\right)_{\text{max}} \frac{2}{\left(\sqrt{1+i_f} + \sqrt{1+i_r}\right)}$$

(3)

where  $I_D$  is the drain current,  $I_S$  is the specific current,  $i_f$  is the normalized forward saturation current (inversion level),  $i_r$  is the normalized reverse saturation current,  $\mu$  is the effective mobility,  $\boldsymbol{C}'_{ox}$  is the oxide capacitance per unit area,  $\phi_t$  is the thermal voltage, W is the effective channel width, L is the effective channel length, n is the slope factor (slightly dependent on gate voltage), and  $g_m = \partial I_D/\partial V_G$   $g_m$  is the transistor transconductance.

The methodology for extracting the effective channel length and width presented here is based on the

determination of the specific current  $I_S$ . The procedure to determine  $I_S$  in this work has been used for the determination of the threshold voltage in a companion paper [6]. For the sake of self-containment of this paper, we will describe briefly, in the next Section, the methodology we have employed to extract the specific current.

## 3 DETERMINATION OF SPECIFIC CURRENT

The determination of the specific current requires a single current-voltage characteristic, from which the transconductance-to-current ratio is calculated. As readily noted from (3) the maximum value of  $g_m/I_D$ , which is equal to  $1/(n\varphi_t)$ , occurs in deep weak inversion, i.e.,  $i_{f(r)} \!\!<\!\!<\!\!1$ . For a fixed value of the drain-to-source voltage, the transconductance-to-current ratio departs from its maximum value in weak inversion by a factor that depends only on the inversion level  $i_f$ , as shown in [6]. Using this concept, we have employed the following methodology for extracting  $I_S$

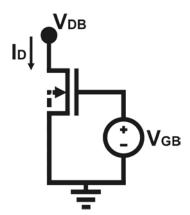

(i) Connect the test device as shown in Fig.1.  $V_{DS}$  must be a small value ( $2\phi_t$  or below) to avoid the influence of high longitudinal electrical fields in the device under test. We have chosen  $V_{DS} = \phi_t/2$  and  $V_{SB} = 0$ .

Fig.1: Circuit configuration for measuring the commonsource characteristics

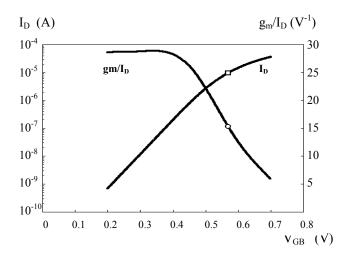

Fig.2. Measured common source characteristics and transconductance-current ratio for  $V_{DS}=13~\text{mV}\cong \varphi_{t}/2$  and  $V_{SB}=0.$  Circle (o):  $g_m/I_D=0.5310(g_m/I_D)_{max};$  square:  $I_D=I_D^*.$   $L_m=1.2\mu\text{m}$  (mask channel length),  $W_m=120~\mu\text{m}$  (mask channel width). TSMC - 0.35  $\mu\text{m}$  technology.

- (ii) Measure the  $I_D$  vs  $V_{GB}$  characteristic for  $V_{DS} = \phi_t/2$  and  $V_{SB} = 0$  (Fig.2).

- (iii) Plot the  $g_m/I_D$  vs  $V_{GB}$  characteristic (Fig.2) and determine  $(g_m/I_D)_{max}$ .

- (iv) Determine the drain current  $I_D^*$  (square in Fig.2) such that  $g_m/I_D = 0.5310(g_m/I_D)_{max}$  (circle in Fig. 2). The specific current  $I_S = 1.135I_D^*$ .

## 4 EXTRACTION OF THE EFFECTIVE CHANNEL LENGTH AND WIDTH

If the methodology for extracting  $I_s$  is performed for several large-width devices with different channel lengths, the following steps lead to the evaluation of the channel length shift  $\Delta L = L_m - L$ , where  $L_m$  is the mask channel length:

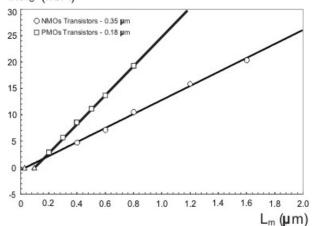

(i) Plot the reciprocal of the measured specific current per unit width vs. mask channel length, i.e.,  $W/I_S$  vs.  $L_m$  (circles in Fig.3).

## W/Is (m/A)

Fig.3. Reciprocal of the specific current per unit width vs. mask channel length. Circles/squars extracted values of W/Is; solid line: fitting straight-line; triangle:  $L_m = \Delta L$ . Measurements were taken from NMOS devices fron TSMC 0.35  $\mu$ m CMOS technology, and PMOS devices fron TSMC 0.18 $\mu$ m CMOS technology.

- (ii ) Interpolate a straight-line that best fits the points in (i) (solid line in Fig.3).

- (iii) If W/I<sub>S</sub> = a L<sub>m</sub> + b is the straight-line referred to in (ii), then  $b/a = -\Delta L$  and  $a^{\text{-1}} = I_{\text{SQ}} \cong 80$  nA is the sheet normalization current (4, 5) for the NMOS transistors, which is in close agreement with technological data for the TSMC 0.35  $\mu$ m CMOS technology.

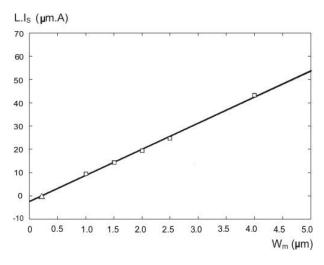

Fig.4: Specific current length product vs. mask channel width. Squares: extracted values of L.I<sub>S</sub>; solid line: fitted straight-line; triangle:  $W_m = \Delta W$ . Measurements were taken on NMOS devices fabricated on TSMC 0.35  $\mu$ m CMOS technology.

Similarly, the shift of the channel width  $\Delta W = W_m - W$  may be evaluated through the fitting of a straight-line to the plot of L.I<sub>S</sub> vs.  $W_m$ , where I<sub>S</sub> is extracted for several devices with different channel widths, as shown in Fig.4.

## 5 EXPERIMENTAL RESULTS

Measurements of the common-source characteristic with  $V_{SB}=0$  and  $V_{DS}=13$  mV, have been accomplished for five NMOS transistors and five PMOS transistors with mask channel lengths of 0.4, 0.6, 0.8, 1.2, 1.6  $\mu m$  and  $W_m/L_m=100;$  five N MOS transistors and five PMOS transistors with mask channel widths of 1.0, 1.5, 2.0, 2.5, 4.0  $\mu m$  and  $L_m=1.2$   $\mu m$ . The aspect ratio for these transistors is 125. The extracted values of  $I_S, \Delta L$  and  $\Delta W$  are shown in Tables 1 and 2.

Table 1: Experimental results for the extraction of the effective channel length.

| 0110001,0 0110111101 10118111.   |       |       |       |       |       |            |  |

|----------------------------------|-------|-------|-------|-------|-------|------------|--|

| $L_{m}\left(\mu m\right)$        | 0.4   | 0.6   | 0.8   | 1.2   | 1.6   | ΔL<br>(μm) |  |

| I <sub>S</sub> (μA) N<br>channel | 9.593 | 9.499 | 8.615 | 8.591 | 8.918 | 0.032      |  |

| I <sub>S</sub> (μA) P channel    | 1.659 | 1.728 | 1.682 | 1.672 | 1.730 | 0.017      |  |

Table 2: Experimental results for the extraction of the effective channel width.

| $W_{m} (\mu m)$                  | 1     | 1.5   | 2     | 2.5    | 4      | ΔW<br>(μm) |

|----------------------------------|-------|-------|-------|--------|--------|------------|

| I <sub>s</sub> (μA) N<br>channel | 9.574 | 9.846 | 9.840 | 10.070 | 10.830 | 0.202      |

| I <sub>S</sub> (μA) P channel    | 1.520 | 1.674 | 1.829 | 2.030  | 2.133  | 0.403      |

#### **SUMMARY**

The methodology described here provides a fast and reliable determination of the effective channel length and width, which is independent of the extraction of the threshold voltage, on the contrary of several methodologies. Since the measurements are taken in moderate inversion, the parameter extraction does not suffer from errors introduced by extrinsic resistances. Biasing the test devices in the linear region avoids the influence of phenomena such as mobility degradation and channel-length modulation. The experimental results have shown to be in close agreement with the model employed to extract the effective channel length and width.

#### **ACKNOWLEDGMENTS**

The authors would like to thank CAPES and CNPq for the financial support and the MOSIS Educational Program for supplying the test devices.

## **REFERENCES**

- [1] Y. Taur, IEEE Transactions on Electron Devices, 47, 160, 2000.

- [2] K. K. Ng and J. R. Brews, IEEE Circuits and Devices, 11, 33, 1990.

- [3] S. Biesemans, M. Hendriks, S. Kubicek, and K. de Meyer, IEEE Transactions on Electron Devices, 45, 1310, 1998.

- [4] A.I.A. Cunha, M.C. Schneider, and C. Galup-Montoro, IEEE J. Solid-State Circuits, 33, 1510, 1998.

- [5] C. Galup-Montoro, M.C. Schneider and A.I.A. Cunha, in "Low Voltage/Low-Power Integrated Circuits and Systems", E. Sánchez-Sinencio and A. Andreou, Editors, p.7, IEEE Press, 1999.

- [6] A. I. A. Cunha, M. C. Schneider, C. Galup-Montoro, C. D. C. Caetano, and M. B. Machado, "Unambiguous extraction of threshold voltage based on the transconductance-to-current ratio", submitted to *Nanotech 2005*.